### 32-bit RISC Microcontroller

# FR30 MB91101 Series

## MB91101/MB91101A

#### DESCRIPTION

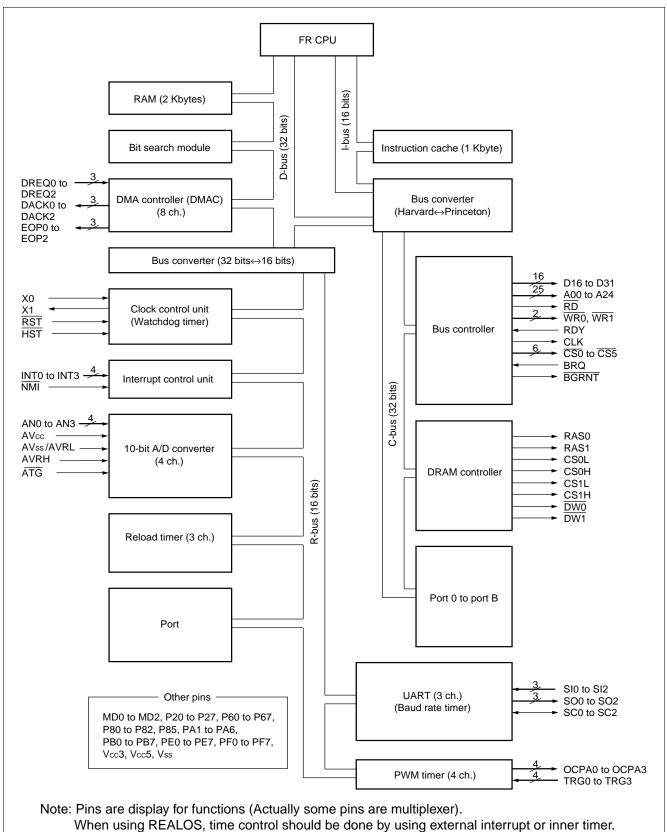

The MB91101 and MB91101A are a standard single-chip microcontroller constructed around the 32-bit RISC CPU (FR\* family) core with abundant I/O resources and bus control functions optimized for high-performance/ high-speed CPU processing for embedded controller applications. To support the vast memory space accessed by the 32-bit CPU, the MB91101 and MB91101A normally operate in the external bus access mode and executes instructions on the internal 1 Kbyte cache memory and 2 Kbytes RAM for enhanced performance.

The MB91101 and MB91101A are optimized for applications requiring high-performance CPU processing such as navigation systems, high-performance FAXs and printer controllers.

\*: FR Family stands for FUJITSU RISC controller.

#### ■ FEATURES

#### FR CPU

- 32-bit RISC, load/store architecture, 5-stage pipeline

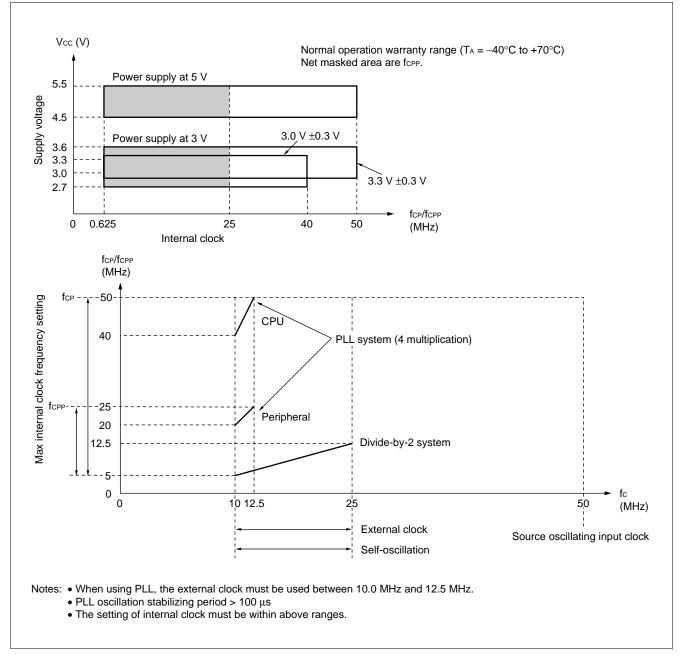

- Operating clock frequency: Internal 50 MHz/external 25 MHz (PLL used at source oscillation 12.5 MHz)

- General purpose registers: 32 bits × 16

- 16-bit fixed length instructions (basic instructions), 1 instruction/1 cycle

- Memory to memory transfer, bit processing, barrel shifter processing: Optimized for embedded applications

- Function entrance/exit instructions, multiple load/store instructions of register contents, instruction systems supporting high level languages

#### PACKAGES

- · Register interlock functions, efficient assembly language coding

- · Branch instructions with delay slots: Reduced overhead time in branch executions

- Internal multiplier/supported at instruction level

- Signed 32-bit multiplication: 5 cycles Signed 16-bit multiplication: 3 cycles

- Interrupt (push PC and PS): 6 cycles, 16 priority levels

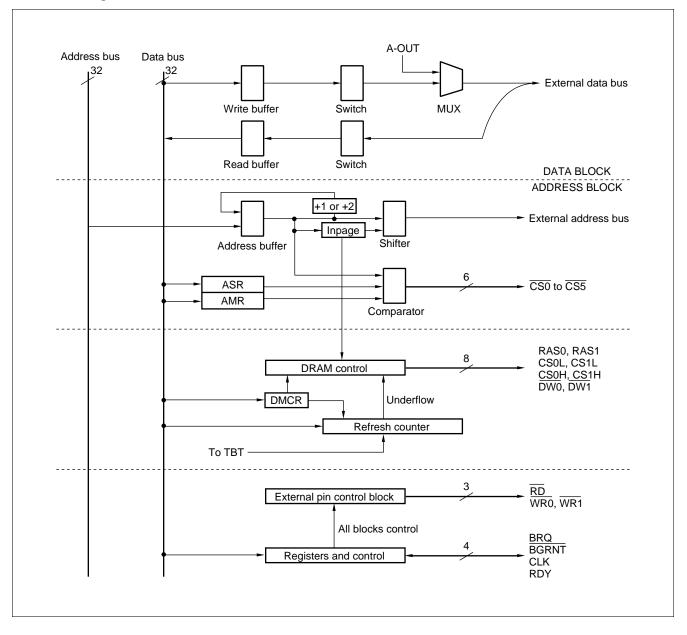

#### **External bus interface**

- Clock doubler: Internal 50 MHz, external bus 25 MHz operation

- 25-bit address bus (32 Mbytes memory space)

- 8/16-bit data bus

- Basic external bus cycle: 2 clock cycles

- Chip select outputs for setting down to a minimum memory block size of 64 Kbytes: 6

- Interface supported for various memory technologies DRAM interface (area 4 and 5)

- Automatic wait cycle insertion: Flexible setting, from 0 to 7 for each area

- Unused data/address pins can be configured as input/output ports.

- Little endian mode supported (Select 1 area from area 1 to 5)

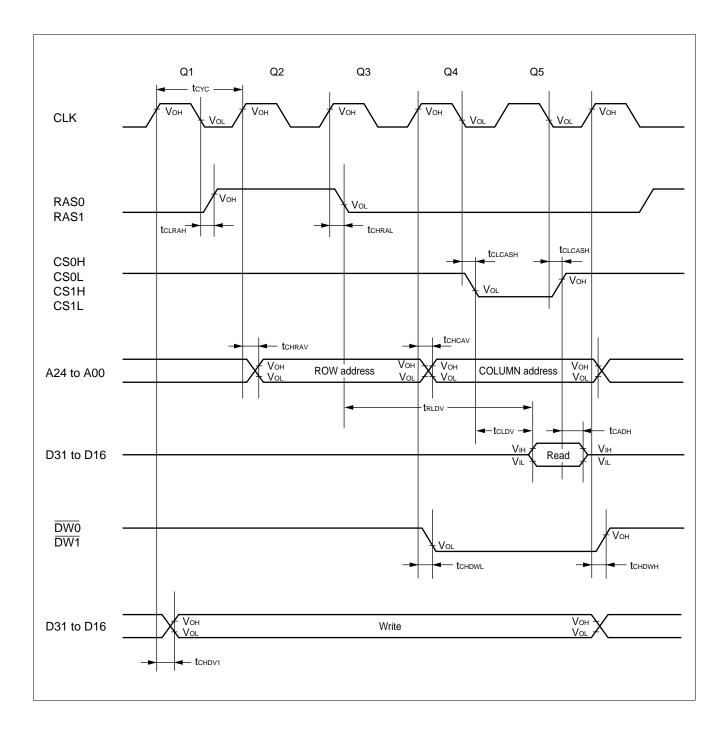

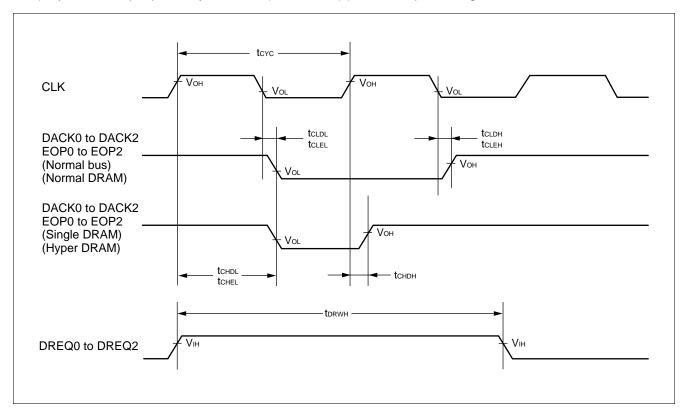

#### **DRAM** interface

- 2 banks independent control (area 4 and 5)

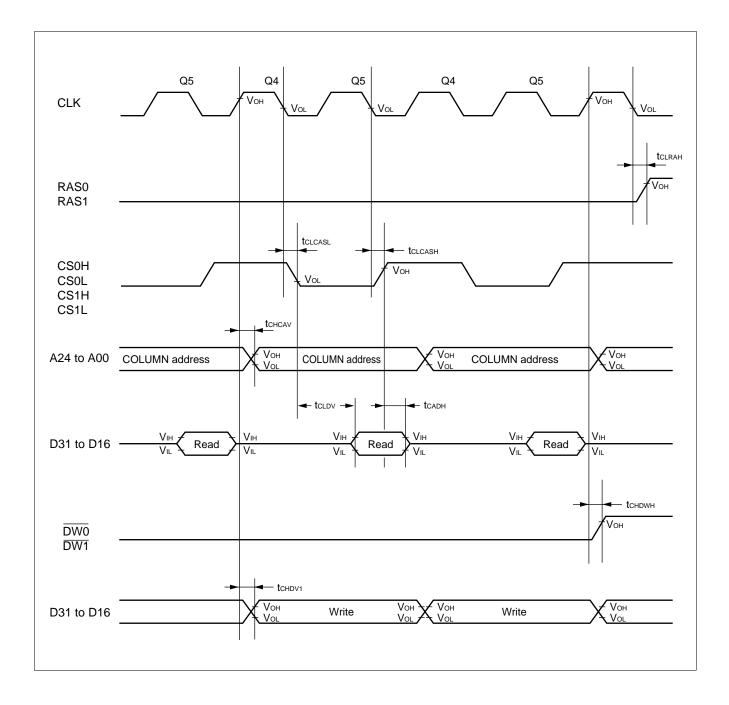

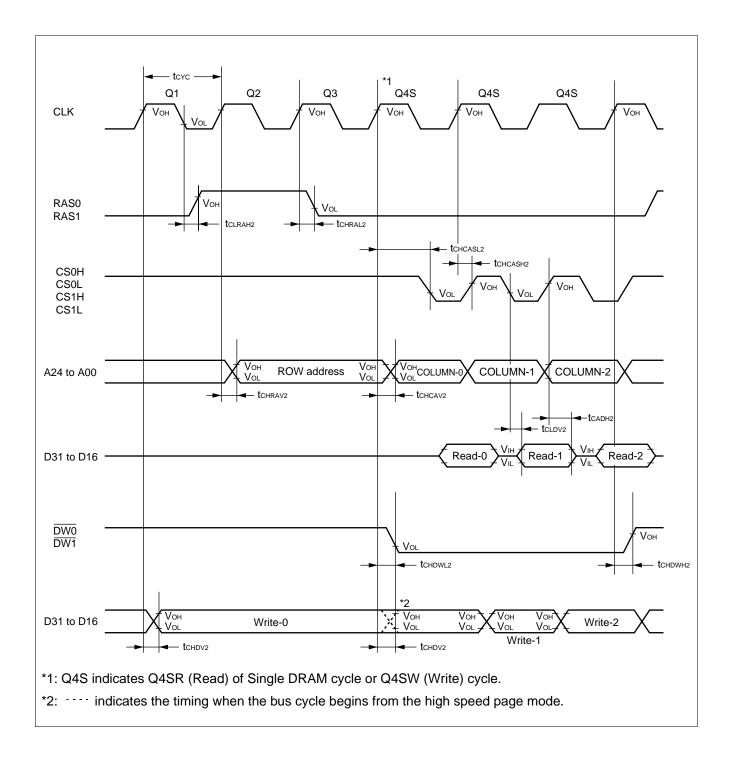

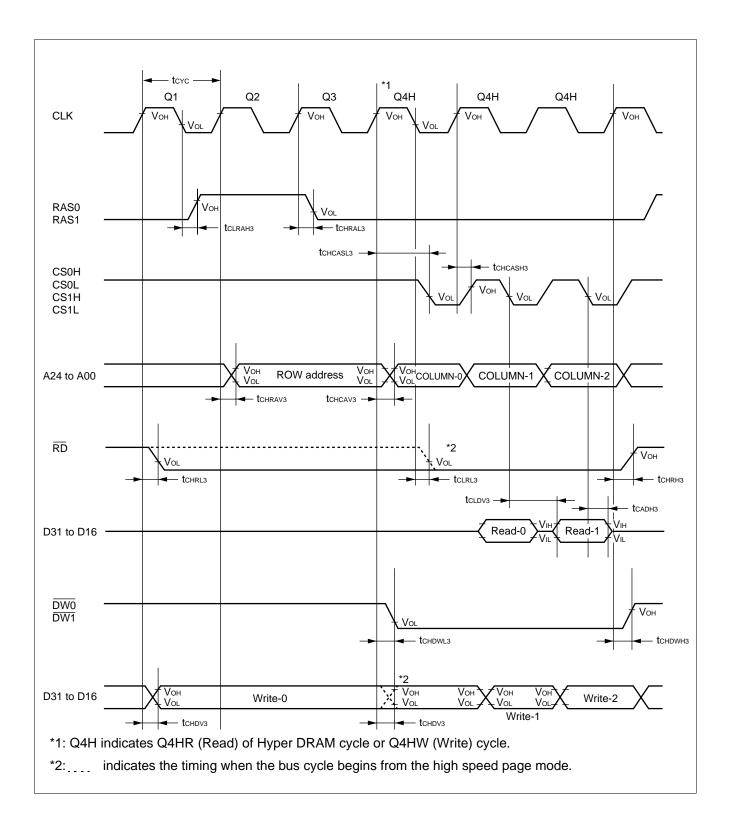

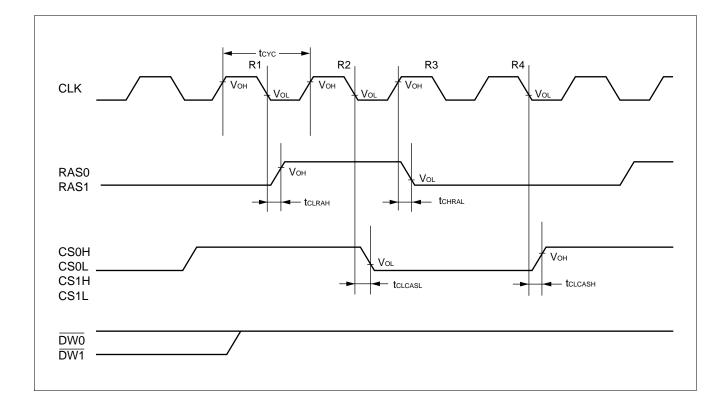

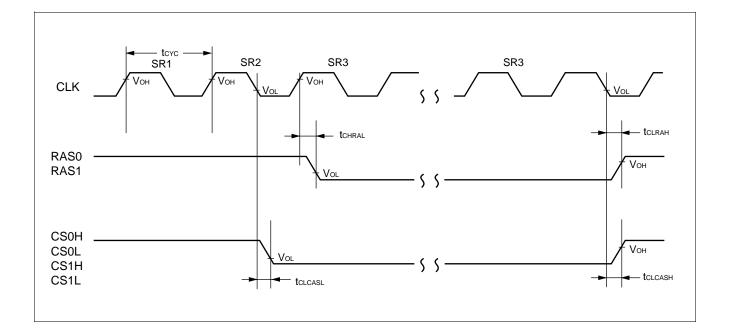

- Normal mode (double CAS DRAM)/high-speed page mode (single CAS DRAM)/Hyper DRAM

- Basic bus cycle: Normally 5 cycles, 2-cycle access possible in high-speed page mode

- Programmable waveform: Automatic 1-cycle wait insertion to RAS and CAS cycles

- DRAM refresh CBR refresh (interval time configurable by 6-bit timer) Self-refresh mode

- Supports 8/9/10/12-bit column address width

- 2CAS/1WE, 2WE/1CAS selective

#### **Cache memory**

- 1-Kbyte instruction cache memory

- 32 block/way, 4 entry(4 word)/block

- 2 way set associative

- · Lock function: For specific program code to be resident in cashe memory

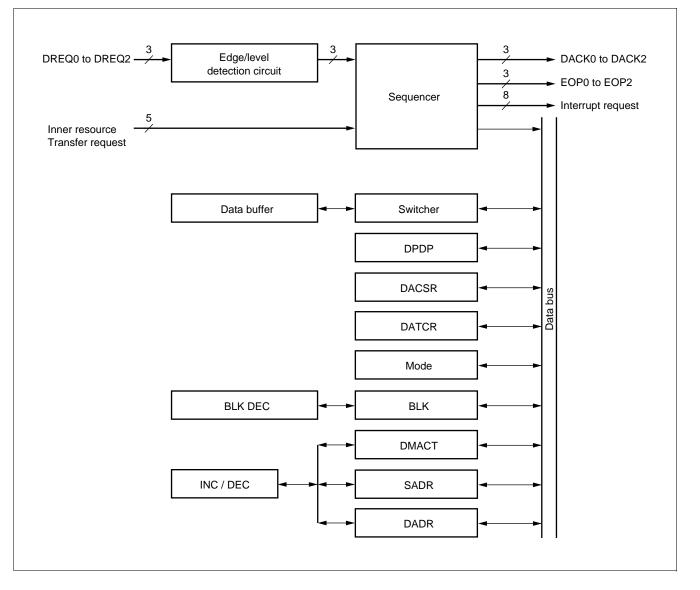

#### **DMA controller (DMAC)**

- 8 channels

- Transfer incident/external pins/internal resource interrupt requests

- Transfer sequence: Step transfer/block transfer/burst transfer/continuous transfer

- Transfer data length: 8 bits/16 bits/32 bits selective

- NMI/interrupt request enables temporary stop operation.

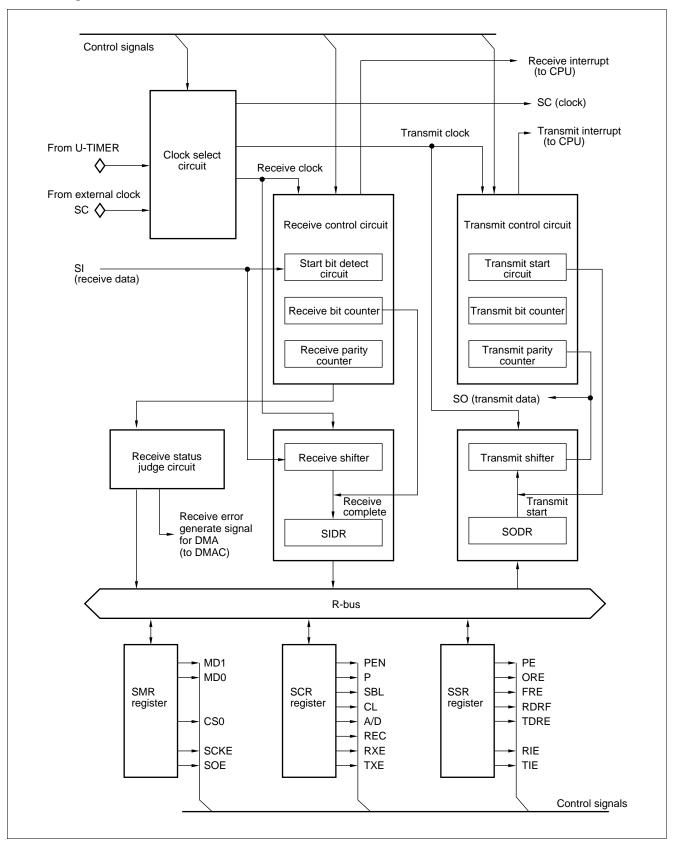

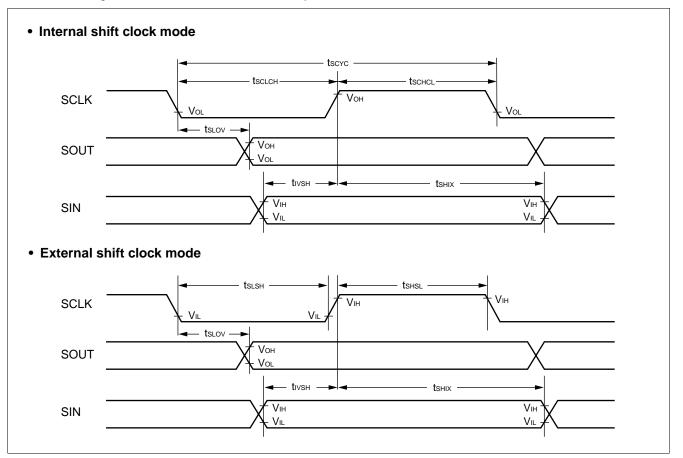

#### UART

- 3 independent channels

- Full-duplex double buffer

- Data length: 7 bits to 9 bits (non-parity), 6 bits to 8 bits (parity)

- Asynchronous (start-stop system), CLK-synchronized communication selective

- Multi-processor mode

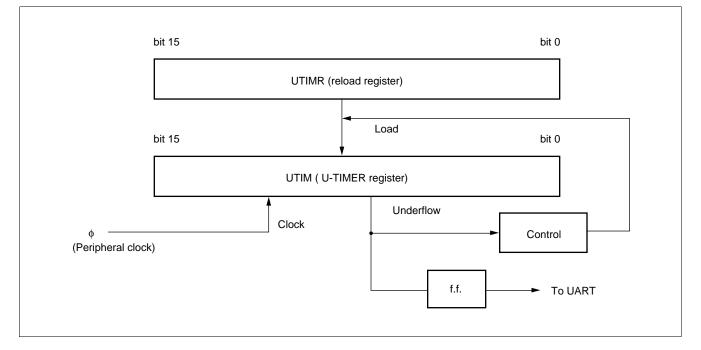

- Internal 16-bit timer (U-TIMER) operating as a proprietary baud rate generator: Generates any given baud rate

- External clock can be used as a transfer clock.

- Error detection: Parity, frame, overrun

#### (Continued)

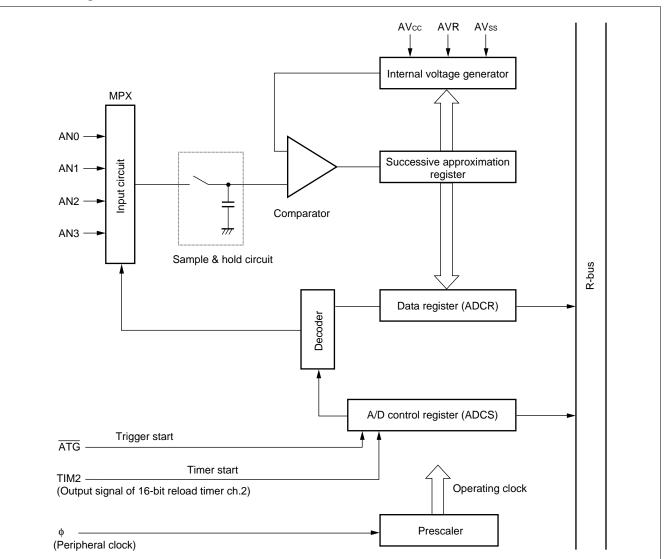

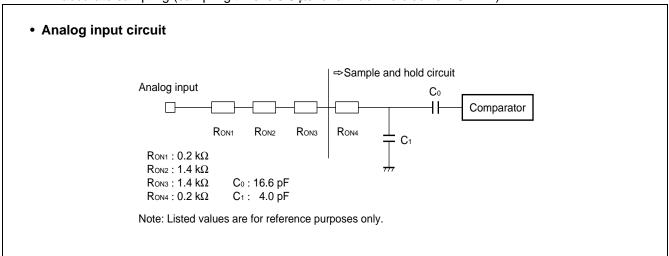

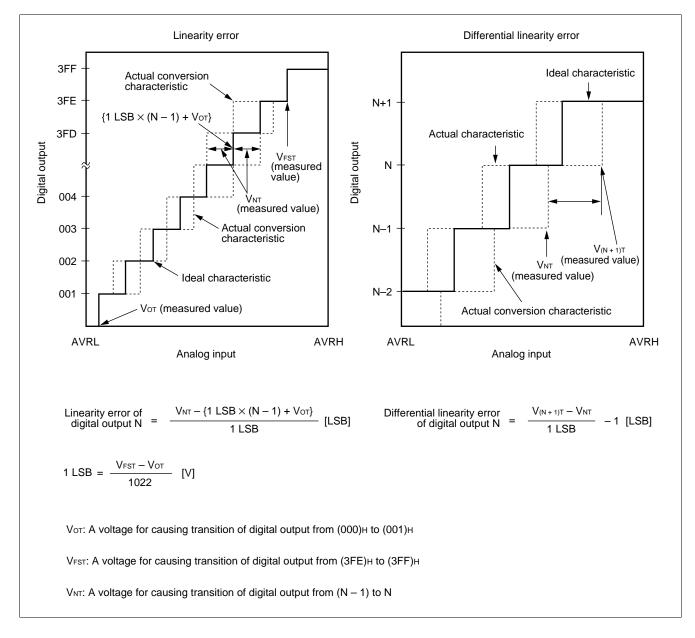

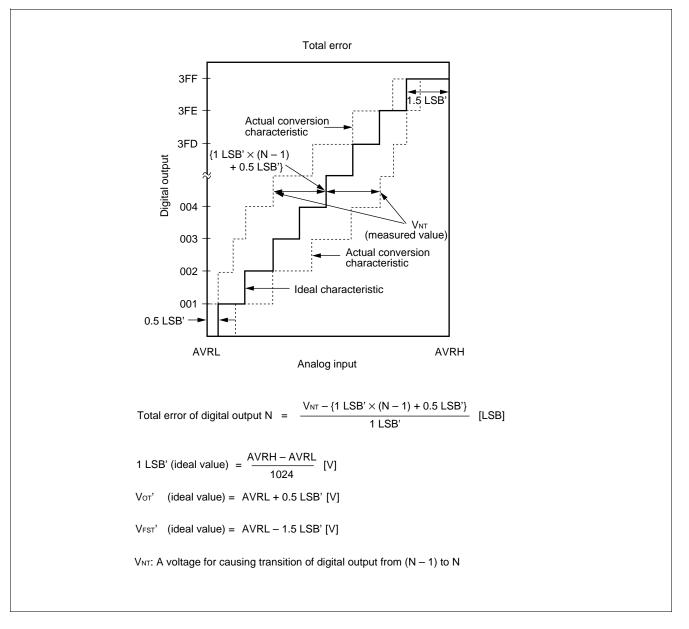

#### 10-bit A/D converter (successive approximation conversion type)

- 10-bit resolution, 4 channels

- Successive approximation type: Conversion time of 5.6  $\mu s$  at 25 MHz

- Internal sample and hold circuit

- Conversion mode: Single conversion/scanning conversion/repeated conversion/stop conversion selective

- Start: Software/external trigger/internal timer selective

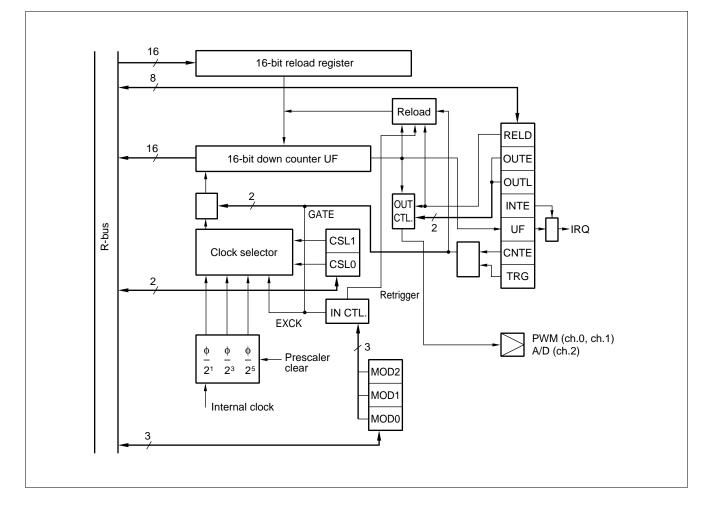

#### 16-bit reload timer

- 3 channels

- Internal clock: 2 clock cycle resolution, divide by 2/8/32 selective

#### Other interval timers

- 16-bit timer: 3 channels (U-TIMER)

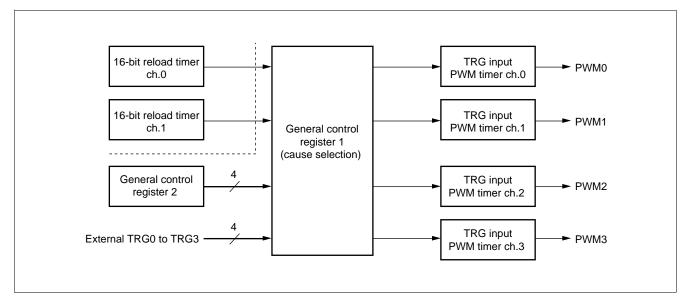

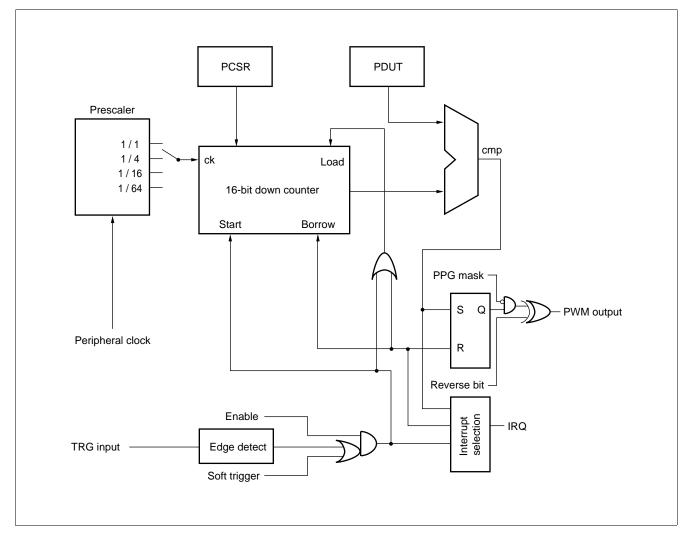

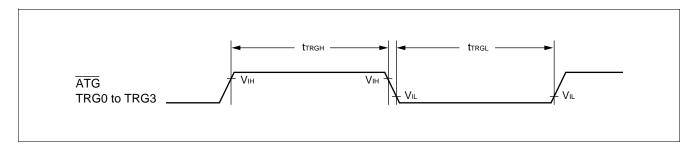

- PWM timer: 4 channels

- Watchdog timer: 1 channel

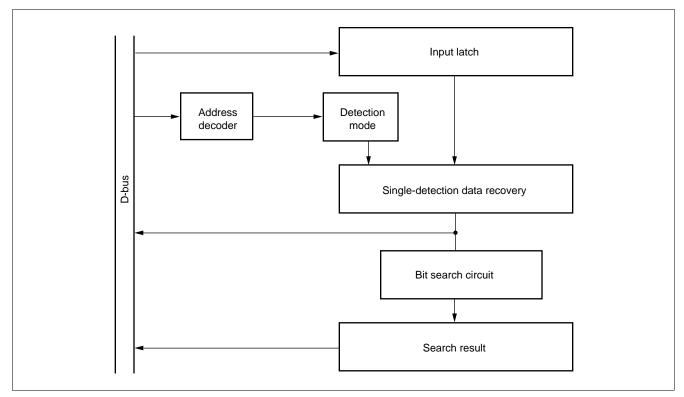

#### Bit search module

First bit transition "1" or "0" from MSB can be detected in 1 cycle.

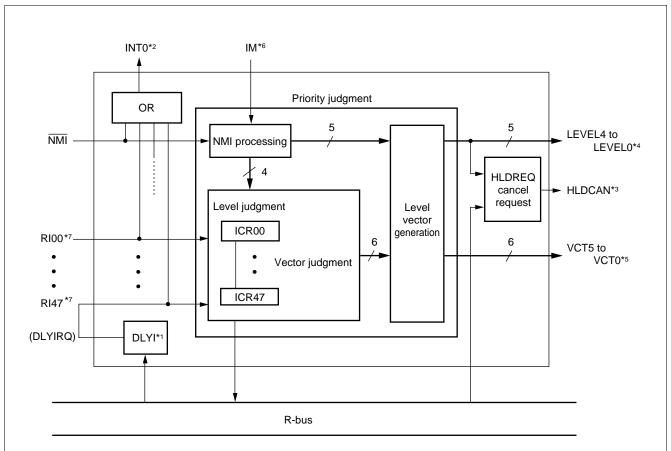

#### Interrupt controller

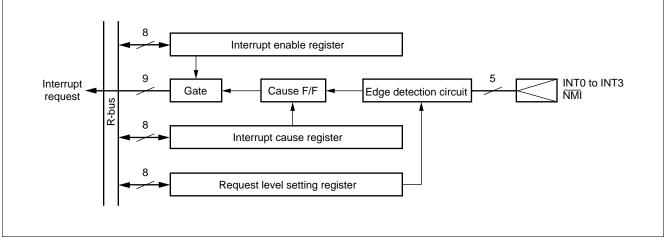

- External interrupt input: Non-maskable interrupt (NMI), normal interrupt × 4 (INT0 to INT3)

- Internal interrupt incident:UART, DMA controller (DMAC), A/D converter, U-TIMER and delayed interrupt module

- Priority levels of interrupts are programmable except for non-maskable interrupt (in 16 steps).

#### Others

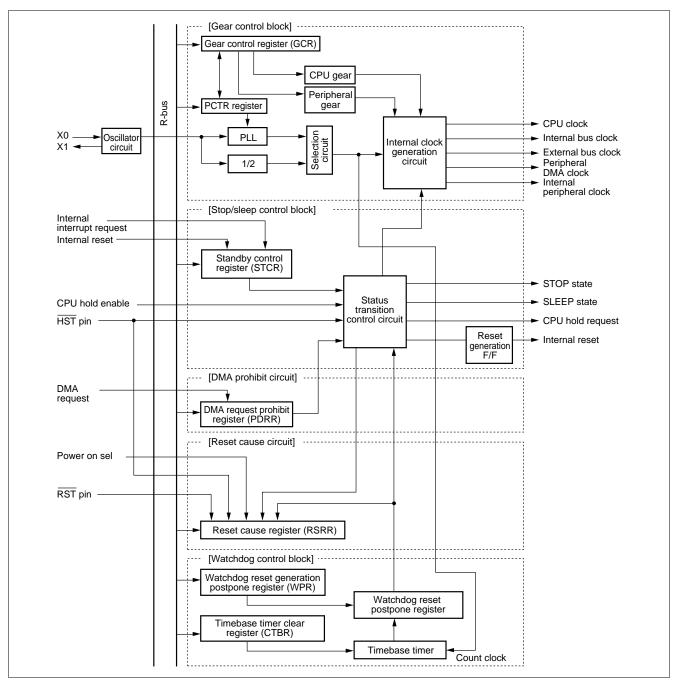

- Reset cause: Power-on reset/hardware standby/watchdog timer/software reset/external reset

- Low-power consumption mode: Sleep mode/stop mode

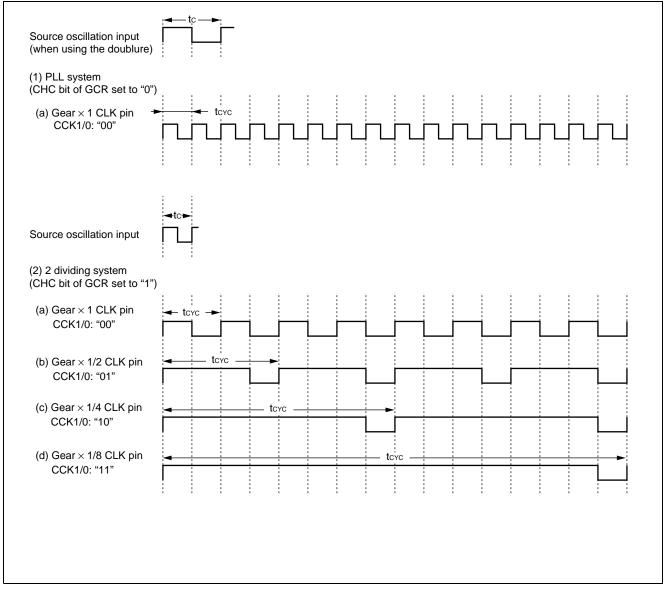

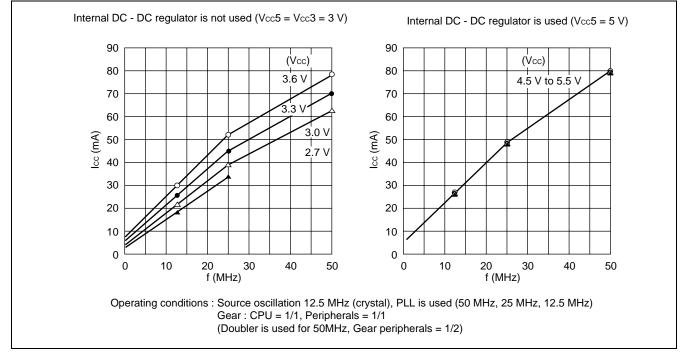

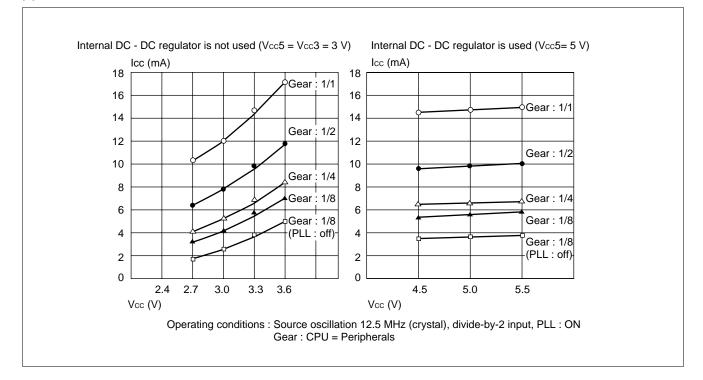

- Clock control

- Gear function: Operating clocks for CPU and peripherals are independently selective. Gear clock can be selected from 1/1, 1/2, 1/4 and 1/8 (or 1/2, 1/4, 1/8 and 1/16). However, operating frequency for peripherals is less than 25 MHz.

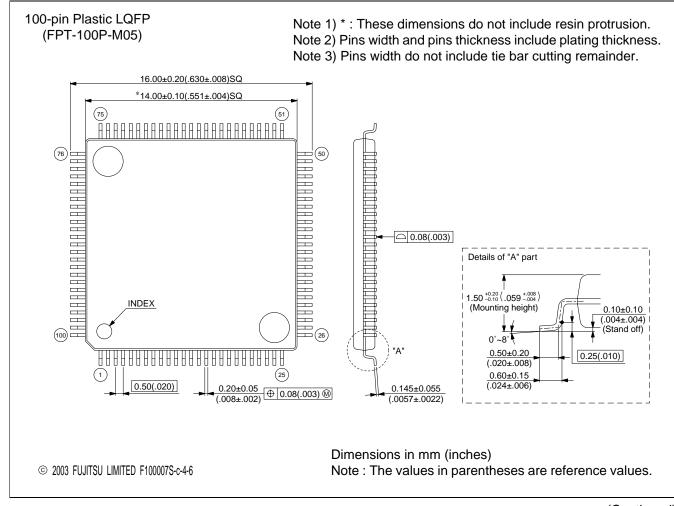

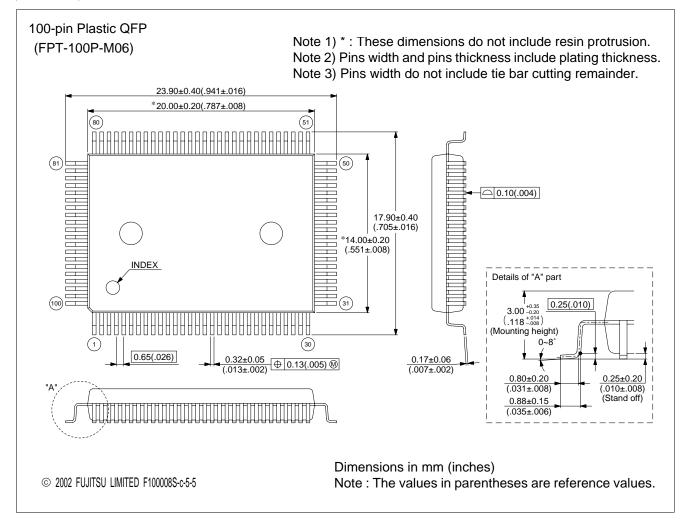

- Packages: LQFP-100 and QFP-100

- CMOS technology (0.35 μm)

- · Power supply voltage

- 5 V: CPU power supply 5.0 V ±10% (internal regulator)

- A/D power supply 2.7 V to 3.6 V

- 3 V: CPU power supply 2.7 V to 3.6 V (without internal regulator) A/D power supply 2.7 V to 3.6 V

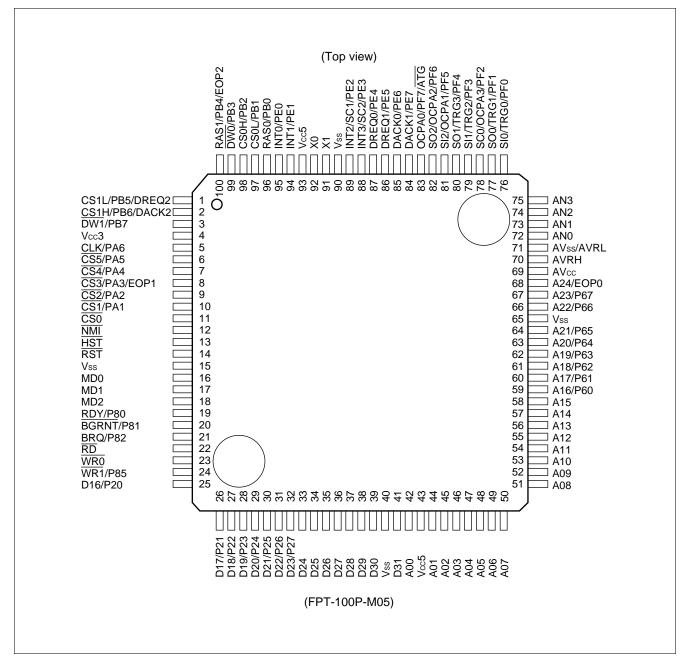

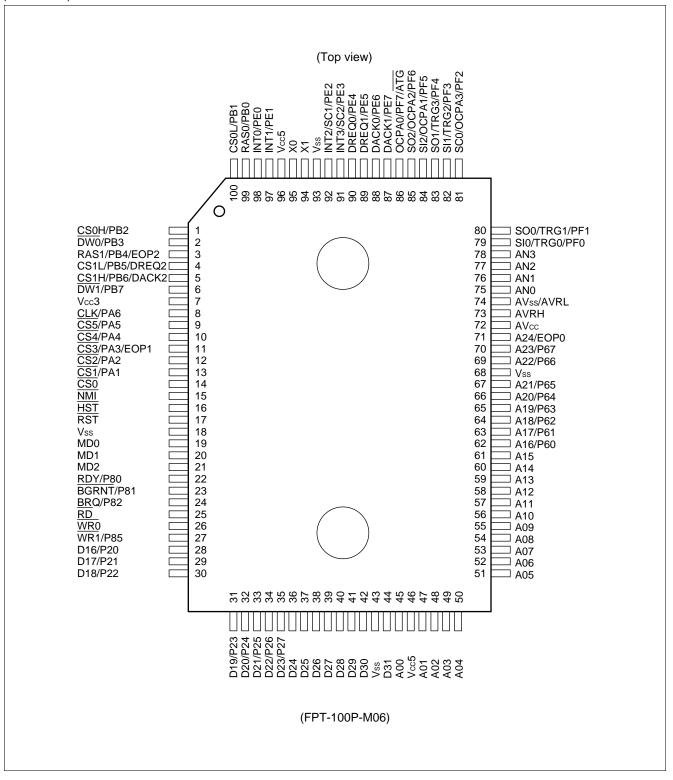

#### PIN ASSIGNMENT

#### ■ PIN DESCRIPTION

| Pin              | no.              | D:                         | Circuit |                                                                                                                             | Decerintian                                |                         |  |  |

|------------------|------------------|----------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------|--|--|

| LQFP*1           | QFP*2            | Pin name                   | type    | Description                                                                                                                 |                                            |                         |  |  |

|                  |                  | D16 to D23                 |         | Bit 16 to bit 23 of e                                                                                                       | external data bus                          |                         |  |  |

| 25 to 32         | 28 to 35         | P20 to P27                 | С       | Can be configured as I/O ports when external data bus width is set to 8-bit.                                                |                                            |                         |  |  |

| 33 to 39,<br>41  | 36 to 42,<br>44  | D24 to D30,<br>D31         | С       | Bit 24 to bit 31 of e                                                                                                       | external data bus                          |                         |  |  |

| 42,<br>44 to 58  | 45,<br>47 to 61  | A00,<br>A01 to A15         | F       | Bit 00 to bit 15 of e                                                                                                       | external address bus                       |                         |  |  |

| 59 to 64,<br>66, | 62 to 67,<br>69, | A16 to A21,<br>A22,<br>A23 | F       | Bit 16 to bit 23 of e                                                                                                       | external address bus                       |                         |  |  |

| 67               | 70<br>70         | P60 to P65,<br>P66,<br>P67 |         | Can be configured                                                                                                           | as I/O ports when n                        | ot used as address bus. |  |  |

|                  |                  | A24                        |         | Bit 24 of external a                                                                                                        | address bus                                |                         |  |  |

| 68               | 71               | EOP0                       | L       | Can be configured as DMAC EOP output (ch. 0) when DMAC EOP output is enabled.                                               |                                            |                         |  |  |

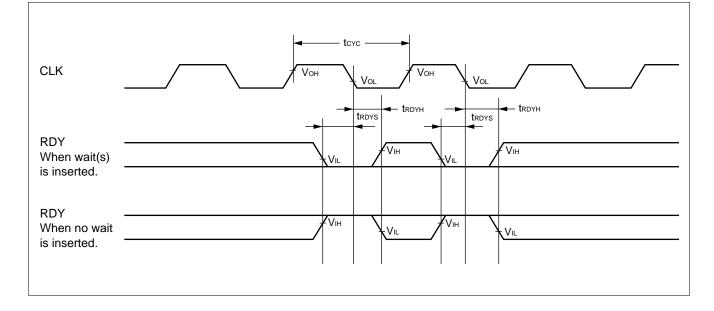

| 19               | 22               | RDY                        | С       | External ready input<br>Inputs "0" when bus cycle is being executed and not complete                                        |                                            |                         |  |  |

|                  | -                | P80                        | 1       | Can be configured                                                                                                           | as a port when RDY                         | ' is not used.          |  |  |

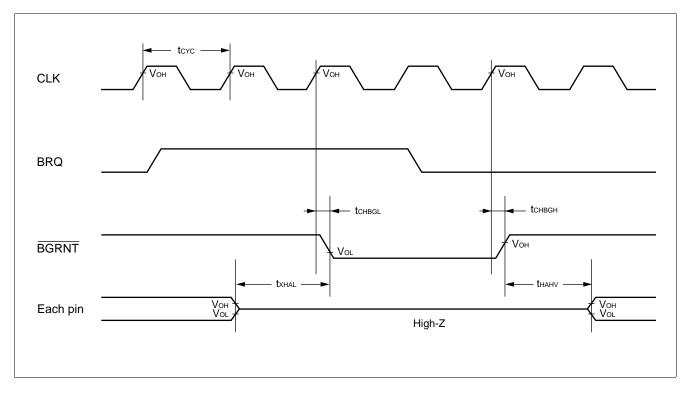

| 20               | 23               | BGRNT                      | F       | External bus release acknowledge output<br>Outputs "L" level when external bus is released.                                 |                                            |                         |  |  |

|                  | -                | P81                        |         | Can be configured                                                                                                           | l as a port when BGR                       | RNT is not used.        |  |  |

| 21               | 24               | BRQ                        | С       | External bus releat Inputs "1" when re                                                                                      | se request input<br>lease of external bus  | is required.            |  |  |

|                  | -                | P82                        |         | Can be configured                                                                                                           | l as a port when BRC                       | ) is not used.          |  |  |

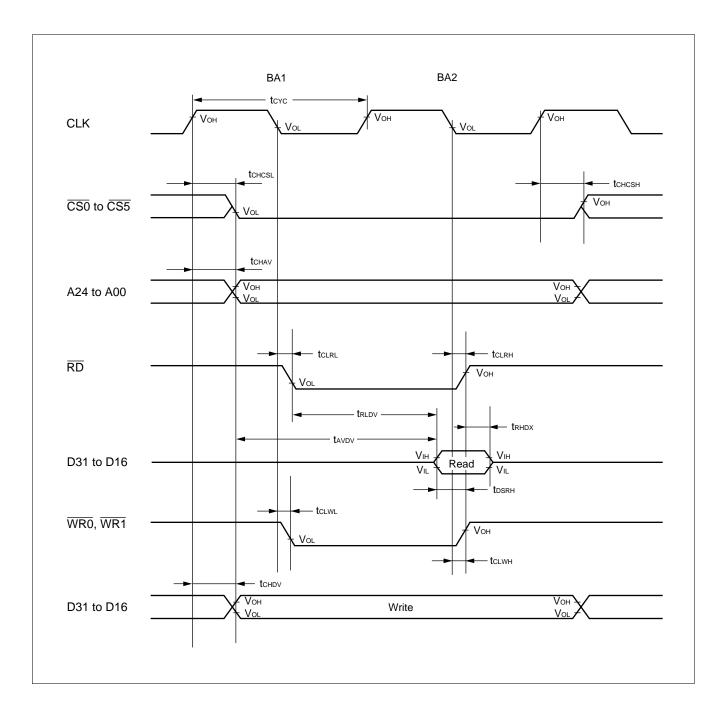

| 22               | 25               | RD                         | L       | Read strobe output                                                                                                          | ut pin for external bus                    | ;<br>;                  |  |  |

| 23               | 26               | WRO                        | L       | Write strobe output pin for external bus<br>Relation between control signals and effective byte locations is<br>as follows: |                                            |                         |  |  |

|                  |                  |                            |         |                                                                                                                             | 16-bit bus width                           | 8-bit bus width         |  |  |

|                  |                  |                            |         | D15 to D08                                                                                                                  | WR0                                        | WR0                     |  |  |

|                  |                  | 27 WR1                     |         | D07 to D00                                                                                                                  | WR1                                        | (I/O port enabled)      |  |  |

| 24               | 27               |                            | F       | WR1 is High-Z du<br>Attach an external<br>width.                                                                            | ring resetting.<br>  pull-up resister wher | n using at 16-bit bus   |  |  |

|                  | -                | P85                        | +       | Can be configured                                                                                                           | as a port when WR1                         | is not used.            |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin    | no.   | D:       | Circuit<br>type | Description                                                                                             |  |

|--------|-------|----------|-----------------|---------------------------------------------------------------------------------------------------------|--|

| LQFP*1 | QFP*2 | Pin name |                 | Description                                                                                             |  |

| 11     | 14    | CS0      | L               | Chip select 0 output ("L" active)                                                                       |  |

| 10     | 10    | CS1      | - F             | Chip select 1 output ("L" active)                                                                       |  |

| 10     | 13    | PA1      |                 | Can be configured as a port when $\overline{CS1}$ is not used.                                          |  |

| 9      | 12    | CS2      | - F             | Chip select 2 output ("L" active)                                                                       |  |

| 9      | 12    | PA2      |                 | Can be configured as a port when $\overline{CS2}$ is not used.                                          |  |

|        |       | CS3      |                 | Chip select 3 output ("L" active)                                                                       |  |

|        |       | PA3      |                 | Can be configured as a port when $\overline{CS3}$ and EOP1 are not used.                                |  |

| 8      | 11    | EOP1     | F               | EOP output pin for DMAC (ch. 1)<br>This function is available when EOP output for DMAC is en-<br>abled. |  |

| 7      | 10    | CS4      | F               | Chip select 4 output ("L" active)                                                                       |  |

| /      | 10    | PA4      |                 | Can be configured as a port when $\overline{CS4}$ is not used.                                          |  |

| 6      | 9     | CS5<br>F |                 | Chip select 5 output ("L" active)                                                                       |  |

| 0      | 9     | PA5      |                 | Can be configured as a port when $\overline{CS5}$ is not used.                                          |  |

| 5      | 8     | CLK      | F               | System clock output<br>Outputs clock signal of external bus operating frequency.                        |  |

|        |       | PA6      |                 | Can be configured as a port when CLK is not used.                                                       |  |

| 96     | 99    | RAS0     | F               | RAS output for DRAM bank 0<br>Refer to the DRAM interface for details.                                  |  |

|        |       | PB0      |                 | Can be configured as a port when RAS0 is not used.                                                      |  |

| 97     | 100   | CS0L     | F               | CASL output for DRAM bank 0<br>Refer to the DRAM interface for details.                                 |  |

|        |       | PB1      |                 | Can be configured as a port when CS0L is not used.                                                      |  |

| 98     | 1     | CS0H     | F               | CASH output for DRAM bank 0<br>Refer to the DRAM interface for details.                                 |  |

|        |       | PB2      |                 | Can be configured as a port when CS0H is not used.                                                      |  |

| 99     | 2     | DW0      | F               | WE output for DRAM bank 0 ("L" active)<br>Refer to the DRAM interface for details.                      |  |

|        |       | PB3      |                 | Can be configured as a port when $\overline{DW0}$ is not used.                                          |  |

|        |       | RAS1     |                 | RAS output for DRAM bank 1<br>Refer to the DRAM interface for details.                                  |  |

| 100    | 3     | PB4      | F               | Can be configured as a port when RAS1 and EOP2 are not used.                                            |  |

|        |       | EOP2     |                 | DMAC EOP output (ch. 2)<br>This function is available when DMAC EOP output is enabled.                  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin       | no.       | Din nome      | Circuit | Description                                                                                                                                                                                                                                                  |  |  |

|-----------|-----------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP*1    | QFP*2     | Pin name      | type    | Description                                                                                                                                                                                                                                                  |  |  |

|           |           | CS1L          |         | CASL output for DRAM bank 1<br>Refer to the DRAM interface for details.                                                                                                                                                                                      |  |  |

|           |           | PB5           |         | Can be configured as a port when CS1L and DREQ2 are not used.                                                                                                                                                                                                |  |  |

| 1         | 4         | DREQ2         | F       | External transfer request input pin for DMA<br>This pin is used for input when external trigger is selected to cause<br>DMAC operation, and it is necessary to disable output for other<br>functions from this pin unless such output is made intentionally. |  |  |

|           |           | CS1H          |         | CASH output for DRAM bank 1<br>Refer to the DRAM interface for details.                                                                                                                                                                                      |  |  |

| 2         | 5         | PB6           | F       | Can be configured as a port when CS1H and DACK2 are not used.                                                                                                                                                                                                |  |  |

| _         | Ū         | DACK2         |         | External transfer request acknowledge output pin for DMAC (ch. 2) This function is available when transfer request output for DMAC is enabled.                                                                                                               |  |  |

| 3         | 6 DW1     |               | F       | WE output for DRAM bank 1 ("L" active)<br>Refer to the DRAM interface for details.                                                                                                                                                                           |  |  |

|           |           | PB7           | -       | Can be configured as a port when $\overline{DW1}$ is not used.                                                                                                                                                                                               |  |  |

| 16 to 18  | 19 to 21  | MD0 to<br>MD2 | G       | Mode pins 0 to 2 MCU basic operation mode is set by these pins. Directly connect these pins with $V_{CC}$ or $V_{SS}$ for use.                                                                                                                               |  |  |

| 92        | 95        | X0            | Α       | Clock (oscillator) input                                                                                                                                                                                                                                     |  |  |

| 91        | 94        | X1            | А       | Clock (oscillator) output                                                                                                                                                                                                                                    |  |  |

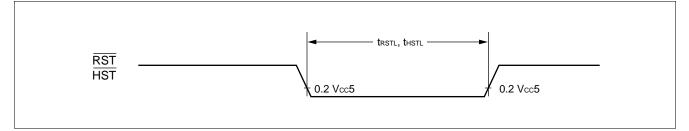

| 14        | 17        | RST           | В       | External reset input                                                                                                                                                                                                                                         |  |  |

| 13        | 16        | HST           | Н       | Hardware standby input ("L" active)                                                                                                                                                                                                                          |  |  |

| 12        | 15        | NMI           | Н       | NMI (non-maskable interrupt pin) input ("L" active)                                                                                                                                                                                                          |  |  |

| 95,<br>94 | 98,<br>97 | INT0,<br>INT1 | F       | External interrupt request input pins<br>These pins are used for input during corresponding interrupt is en-<br>abled, and it is necessary to disable output for other functions from<br>these pins unless such output is made intentionally.                |  |  |

|           |           | PE0,<br>PE1   |         | Can be configured as I/O ports when INT0, INT1 are not used.                                                                                                                                                                                                 |  |  |

|           | 22        | INT2          | _       | External interrupt request input pin<br>This pin is used for input during corresponding interrupt is enabled,<br>and it is necessary to disable output for other functions from this pin<br>unless such output is made intentionally.                        |  |  |

| 89        | 92        | SC1           | F       | Clock I/O pin for UART1<br>Clock output is available when clock output of UART1 is enabled.                                                                                                                                                                  |  |  |

|           |           | PE2           |         | Can be configured as the I/O port when INT2 and SC1 are not used.<br>This function is available when UART1 clock output is disabled.                                                                                                                         |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin no.   |           | Pin name        | Circuit | Description                                                                                                                                                                                                                                                             |  |  |

|-----------|-----------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP*1    | QFP*2     | Pin name        | type    | Description                                                                                                                                                                                                                                                             |  |  |

|           |           | INT3            | _       | External interrupt request input pin<br>This pin is used for input during corresponding interrupt is enabled,<br>and it is necessary to disable output for other functions from this pin<br>unless such output is made intentionally.                                   |  |  |

| 88        | 91        | SC2             | F       | UART2 clock I/O pin<br>Clock output is available when UART2 clock output is enabled.                                                                                                                                                                                    |  |  |

|           |           | PE3             |         | Can be configured as the I/O port when INT3 and SC2 are not used.<br>This function is available when UART2 clock output is disabled.                                                                                                                                    |  |  |

| 87,<br>86 | 90,<br>89 | DREQ0,<br>DREQ1 | F       | External transfer request input pins for DMA<br>These pins are used for input when external trigger is selected to<br>cause DMAC operation, and it is necessary to disable output for<br>other functions from these pins unless such output is made inten-<br>tionally. |  |  |

|           |           | PE4,<br>PE5     |         | Can be configured as I/O ports when DREQ0, DREQ1 are not used.                                                                                                                                                                                                          |  |  |

|           | 88        | DACK0           | F       | External transfer request acknowledge output pin for DMAC (ch. 0) This function is available when transfer request output for DMAC is enabled.                                                                                                                          |  |  |

| 85        | 00        | PE6             |         | Can be configured as the I/O port when DACK0 is not used.<br>This function is available when transfer request acknowledge out-<br>put for DMAC or DACK0 output is disabled.                                                                                             |  |  |

| 94        | 87        | DACK1           | F       | External transfer request acknowledge output pin for DMAC (ch. 1)<br>This function is available when transfer request output for DMAC is<br>enabled.                                                                                                                    |  |  |

| 84        | 07        | PE7             |         | Can be configured as the I/O port when DACK1 is not used.<br>This function is available when transfer request output for DMAC or<br>DACK1 output is disabled.                                                                                                           |  |  |

|           |           | SI0             |         | UART0 data input pin<br>This pin is used for input during UART0 is in input operation, and it<br>is necessary to disable output for other functions from this pin un-<br>less such output is made intentionally.                                                        |  |  |

| 76        | 79        | TRG0            | F       | PWM timer external trigger input pin<br>This pin is used for input during PWM timer external trigger is in in-<br>put operation, and it is necessary to disable output for other func-<br>tions from this pin unless such output is made intentionally.                 |  |  |

|           |           | PF0             |         | Can be configured as the I/O port when SI0 and TRG0 are not used.                                                                                                                                                                                                       |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

| Pin no. |       |          | Circuit | Description                                                                                                                                                                                                                                             |  |  |

|---------|-------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP*1  | QFP*2 | Pin name | type    | Description                                                                                                                                                                                                                                             |  |  |

|         |       | SO0      |         | UART0 data output pin<br>This function is available when UART0 data output is enabled.                                                                                                                                                                  |  |  |

| 77      | 80    | TRG1     | F       | PWM timer external trigger input pin<br>This function is available when serial data output of PF1, UART0<br>are disabled.                                                                                                                               |  |  |

|         |       | PF1      |         | Can be configured as the I/O port when SO0 and TRG1 are not<br>used.<br>This function is available when serial data output of UART0 is dis-<br>abled.                                                                                                   |  |  |

|         |       | SC0      |         | UART0 clock I/O pin<br>Clock output is available when UART0 clock output is enabled.                                                                                                                                                                    |  |  |

| 78      | 81    | OCPA3    | F       | PWM timer output pin<br>This function is available when PWM timer output is enabled.                                                                                                                                                                    |  |  |

|         |       | PF2      | +       | Can be configured as the I/O port when SC0 and OCPA3 are not<br>used.<br>This function is available when UART0 clock output is disabled.                                                                                                                |  |  |

|         |       | SI1      | F       | UART1 data input pin<br>This pin is used for input during UART1 is in input operation, and it<br>is necessary to disable output for other functions from this pin un-<br>less such output is made intentionally.                                        |  |  |

| 79      | 82    | TRG2     |         | PWM timer external trigger input pin<br>This pin is used for input during PWM timer external trigger is in in-<br>put operation, and it is necessary to disable output for other func-<br>tions from this pin unless such output is made intentionally. |  |  |

|         |       | PF3      |         | Can be configured as the I/O port when SI1 and TRG2 are not used.                                                                                                                                                                                       |  |  |

|         |       | SO1      |         | UART1 data output pin<br>This function is available when UART1 data output is enabled.                                                                                                                                                                  |  |  |

| 80      | 83    | TRG3     | F       | PWM timer external trigger input pin<br>This function is available when PF4, UART1 data outputs are dis-<br>abled.                                                                                                                                      |  |  |

|         |       | PF4      |         | Can be configured as the I/O port when SO1 and TRG3 are not<br>used.<br>This function is available when UART1 data output is disabled.                                                                                                                  |  |  |

|         |       | SI2      | _       | UART2 data input pin<br>This pin is used for input during UART2 is in input operation, and it<br>is necessary to disable output for other functions from this pin un-<br>less such output is made intentionally.                                        |  |  |

| 81      | 84    | OCPA1    | F       | PWM timer output pin<br>This function is available when PWM timer output is enabled.                                                                                                                                                                    |  |  |

|         |       | PF5      |         | Can be configured as the I/O port when SI2 and OCPA1 are not used.                                                                                                                                                                                      |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

(Continued)

| Pin                     | no.                     | Din nome    | Circuit | Description                                                                                                                                                                                                                                                               |  |  |

|-------------------------|-------------------------|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LQFP*1                  | QFP*2                   | Pin name    | type    | Description                                                                                                                                                                                                                                                               |  |  |

|                         |                         | SO2         |         | UART2 data output pin<br>This function is available when UART2 data output is enabled.                                                                                                                                                                                    |  |  |

| 82                      | 85                      | OCPA2       | F       | PWM timer output pin<br>This function is available when PWM timer output is enabled.                                                                                                                                                                                      |  |  |

|                         |                         | PF6         |         | Can be configured as the I/O port when SO2 and OCPA2 are<br>not used.<br>This function is available when UART2 data output is disabled.                                                                                                                                   |  |  |

|                         |                         | OCPA0       |         | PWM timer output pin<br>This function is available when PWM timer output is enabled.                                                                                                                                                                                      |  |  |

| 83                      | 86                      | PF7         | F       | Can be configured as the I/O port when OCPA0 and ATG are<br>not used.<br>This function is available when PWM timer output is disabled.                                                                                                                                    |  |  |

| 83 80                   |                         | ATG         | - •     | External trigger input pin for A/D converter<br>This pin is used for input when external trigger is selected to<br>cause A/D converter operation, and it is necessary to disable<br>output for other functions from this pin unless such output is<br>made intentionally. |  |  |

| 72 to 75                | 75 to 78                | AN0 to AN3  | D       | Analog input pins of A/D converter                                                                                                                                                                                                                                        |  |  |

| 69                      | 72                      | AVcc        | _       | Power supply pin (Vcc) for A/D converter                                                                                                                                                                                                                                  |  |  |

| 70                      | 73                      | AVRH        |         | Reference voltage input (high) for A/D converter<br>Make sure to turn on and off this pin with potential of AVRH or<br>more applied to AVcc.                                                                                                                              |  |  |

| 71                      | 74                      | AVss / AVRL | _       | Power supply pin (Vss) for A/D converter and reference voltage input pin (low) $\label{eq:voltage}$                                                                                                                                                                       |  |  |

| 43,<br>93               | 46,<br>96               | Vcc5        |         | 5 V power supply pin (Vcc) for digital circuit Always two pins must be connected to the power supply (connect to 3 V power supply when operating at 3 V).                                                                                                                 |  |  |

| 4                       | 7                       | Vcc3        |         | Bypass capacitor pin for internal capacitor.<br>Also connect this pin to 3 V power supply when operating at<br>3 V.                                                                                                                                                       |  |  |

| 15,<br>40,<br>65,<br>90 | 18,<br>43,<br>68,<br>93 | Vss         |         | Earth level (Vss) for digital circuit                                                                                                                                                                                                                                     |  |  |

\*1: FPT-100P-M05

\*2: FPT-100P-M06

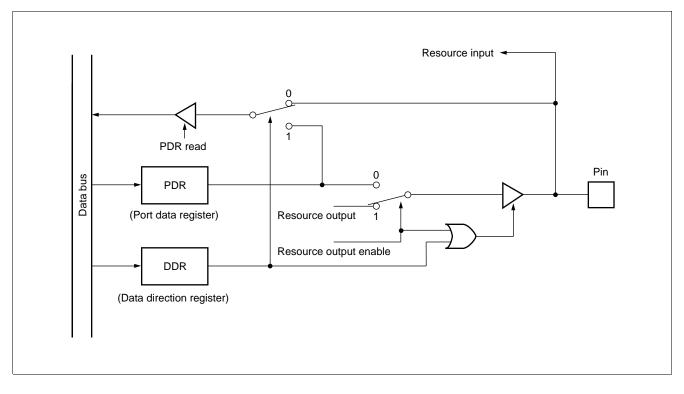

Note: In most of the above pins, I/O ports and resource I/O are multiplexed, e.g. P82 and BRQ. In case of conflict between output of I/O ports and resource I/O, priority is always given to the output of resource I/O.

#### ■ DRAM CONTROL PIN

| Pin name | Data bus '    | 16-bit mode   | Data bus 8-bit mode | Remarks                                            |

|----------|---------------|---------------|---------------------|----------------------------------------------------|

| Fin name | 2CAS/1WR mode | 1CAS/2WR mode | _                   | Remarks                                            |

| RAS0     | Area 4 RAS    | Area 4 RAS    | Area 4 RAS          | Correspondence of "L",                             |

| RAS1     | Area 5 RAS    | Area 5 RAS    | Area 5 RAS          | "H" to lower address 1<br>bit (A0) in data bus 16- |

| CSOL     | Area 4 CASL   | Area 4 CAS    | Area 4 CAS          | bit mode<br>"L": "0"                               |

| CS0H     | Area 4 CASH   | Area 4 WEL    | Area 4 CAS          | "H": "1"<br>CASL:CAS which A0                      |

| CS1L     | Area 5 CASL   | Area 5 CAS    | Area 5 CAS          | corresponds to "0" area<br>CASH:CAS which A0       |

| CS1H     | Area 5 CASH   | Area 5 WEL    | Area 5 CAS          | corresponds to "1" area                            |

| DW0      | Area 4 WE     | Area 4 WEH    | Area 4 WE           | responds to "0" area                               |

| DW1      | Area 5 WE     | Area 5 WEH    | Area 5 WE           | responds to "1" area                               |

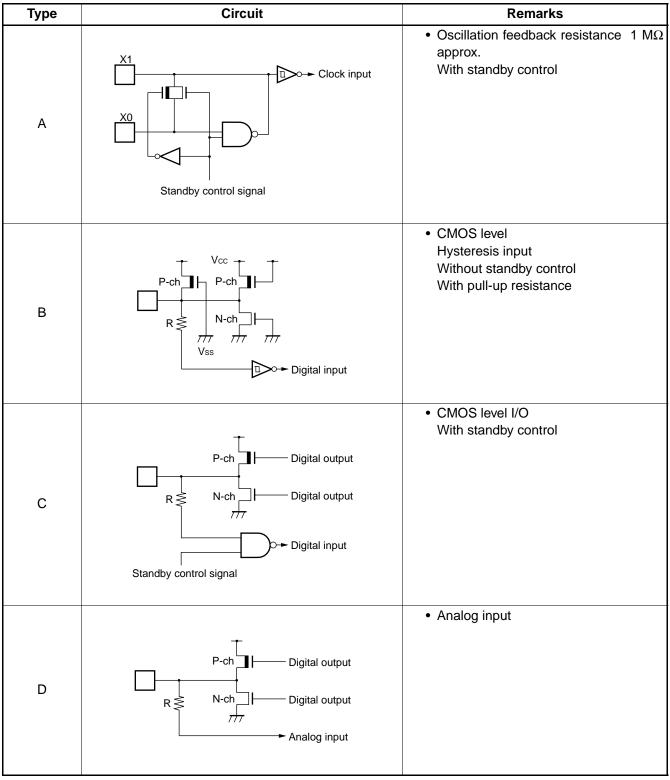

#### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                                                                 | Remarks                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| F    | P-ch Digital output<br>R N-ch Digital output<br>777<br>Digital output<br>777<br>Digital input<br>Standby control signal | <ul> <li>CMOS level output</li> <li>CMOS level<br/>Hysteresis input<br/>With standby control</li> </ul> |

| G    | P-ch<br>R S<br>N-ch<br>TTT<br>TTT<br>Digital input                                                                      | CMOS level input     Without standby control                                                            |

| Н    | P-ch<br>R N-ch<br>777 777<br>Digital input                                                                              | CMOS level     Hysteresis input     Without standby control                                             |

| L    | P-ch Digital output                                                                                                     | CMOS level output                                                                                       |

#### HANDLING DEVICES

#### 1. Preventing Latchup

In CMOS ICs, applying voltage higher than  $V_{cc}$  or lower than  $V_{ss}$  to input/output pin or applying voltage over rating across  $V_{cc}$  and  $V_{ss}$  may cause latchup.

This phenomenon rapidly increases the power supply current, which may result in thermal breakdown of the device. Make sure to prevent the voltage from exceeding the maximum rating.

Take care that the analog power supply (AVcc , AVRH) and the analog input do not exceed the digital power supply (Vcc) when the analog power supply turned on or off.

#### 2. Treatment of Unused Pins

Unused pins left open may cause malfunctions. Make sure to connect them to pull-up or pull-down resistors.

#### 3. External Reset Input

It takes at least 5 machine cycle to input "L" level to the RST pin and to ensure inner reset operation properly.

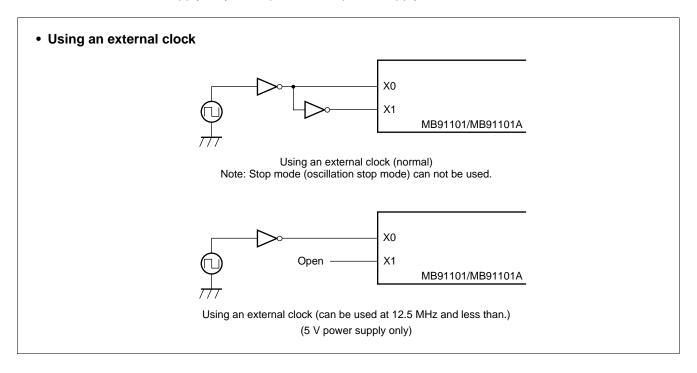

#### 4. Remarks for External Clock Operation

When external clock is selected, supply it to X0 pin generally, and simultaneously the opposite phase clock to X0 must be supplied to X1 pin. However, in this case the stop mode must not be used (because X1 pin stops at "H" output in stop mode).

And it can be used to supply only to X0 pin with 5 V power supply at 12.5 MHz and less than.

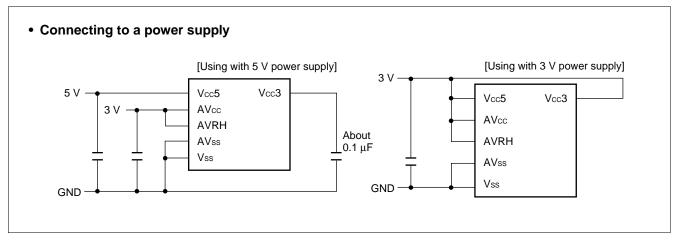

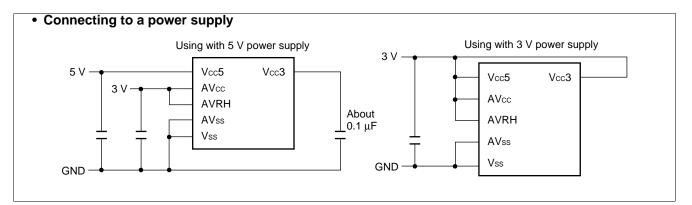

#### 5. Power Supply Pins

When there are several V<sub>cc</sub> and V<sub>ss</sub> pins, each of them is equipotentially connected to its counterpart inside of the device, minimizing the risk of malfunctions such as latch up. To further reduce the risk of malfunctions, to prevent EMI radiation, to prevent strobe signal malfunction resulting from creeping-up of ground level and to observe the total output current standard, connect all V<sub>cc</sub> and V<sub>ss</sub> pins to the power supply or GND. It is preferred to connect V<sub>cc</sub> and V<sub>ss</sub> of the MB91101and MB91101A to power supply with minimal impedance possible.

It is also recommended to connect a ceramic capacitor as a bypass capacitor of about 0.1  $\mu$ F between V<sub>cc</sub> and V<sub>ss</sub> at a position as close as possible to the MB91101 and MB91101A.

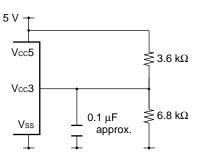

The MB91101 and MB91101A have an internal regulator. When using with 5 V power supply, supply 5 V to Vcc5 pin and make sure to connect about 0.1  $\mu$ F bypass capacitor to Vcc3 pin for regulator. And another 3 V power supply is needed for the A/D convertor. When using with 3 V power supply, connect both Vcc5 pin and Vcc3 pin to the 3 V power supply.

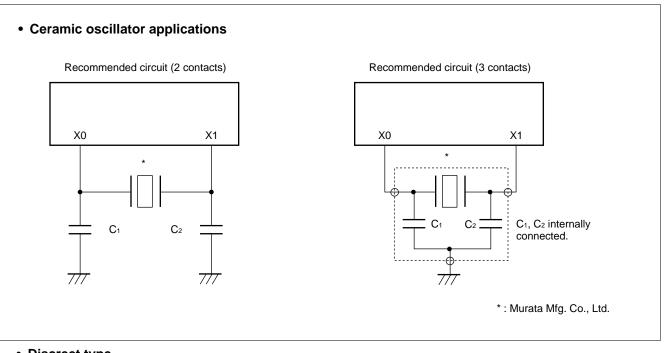

#### 6. Crystal Oscillator Circuit

Noises around X0 and X1 pins may cause malfunctions of the MB91101 and MB91101A. In designing the PC board, layout X0 and X1 pins, crystal oscillator (or ceramic oscillator) and bypass capacitor for grounding as close as possible.

It is strongly recommended to design PC board so that X1 and X0 pins are surrounded by grounding area for stable operation.

#### 7. Turning-on Sequence of A/D Converter Power Supply and Analog Input

Make sure to turn on the digital power supply (Vcc) before turning on the A/D converter (AVcc, AVRH) and applying voltage to analog input (AN0 to AN3).

Make sure to turn off digital power supply after power supply to A/D converters and analog inputs have been switched off. (There are no such limitations in turning on power supplies. Analog and digital power supplies may be turned on simultaneously.) Make sure that AVRH never exceeds AVcc when turning on/off power supplies.

#### 8. Fluctuation of Power Supply Voltage

Warranty range for normal operation against fluctuation of power supply voltage V<sub>cc</sub> is as given in rating. However, sudden fluctuation of power supply voltage within the warranty range may cause malfunctions. It is recommended to make every effort to stabilize the power supply voltage to IC. It is also recommended that by controlling power supply as a reference of stabilizing, V<sub>cc</sub> ripple fluctuation (P-P value) at the commercial frequency (50 Hz to 60 Hz) should be less than 10% of the standard V<sub>cc</sub> value and the transient regulation should be less than 0.1 V/ms at instantaneous deviation like turning off the power supply.

#### 9. Mode Setting Pins (MD0 to MD2)

Connect mode setting pins (MD0 to MD2) directly to  $V_{CC}$  or  $V_{SS}$ .

Arrange each mode setting pin and  $V_{cc}$  or  $V_{ss}$  patterns on the printed circuit board as close as possible and make the impedance between them minimal to prevent mistaken entrance to the test mode caused by noises.

#### 10. Internal DC Regulator

Internal DC regulator stops in stop mode. When the regulator stops owing to the increase of inner leakage current (ICCH) in stop mode, malfunction caused by noise or any troubles about power supply in normal operation, the internal 3 V power supply voltage may decrease less than the warranty range for normal operation. So when using the internal regulator and stop mode with 5 V power supply, never fail to support externally so that 3 V power supply voltage might not decrease. However, even in such a case, the internal regulator can be restarted

by inputting the reset procedure. (In this case, set the reset to "L" level within the oscillation stabilizing waiting time.)

#### • Using STOP mode with 5 V power supply

#### 11. Pin Condition at Turning on the Power Supply

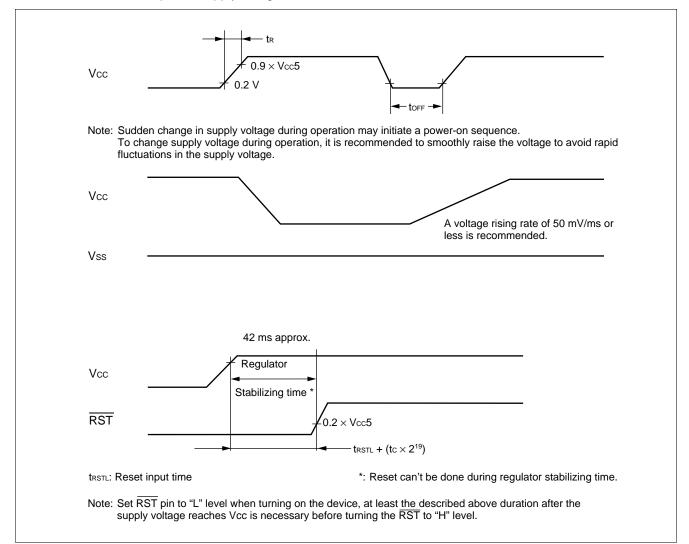

The pin condition at turning on the power supply is unstable. The circuit starts being initialized after turning on the power supply and then starting oscillation and then the operation of the internal regulator becomes stable. So it takes about 42 ms for the pin to be initialized from the oscillation starting at the source oscillation 12.5 MHz. Take care that the pin condition may be output condition at initial unstable condition.

(With the MB91101A, however, initalization can be achieved in less than about 42 ms after turning on the internal power supply by maintaining the RST pin at "L" level.)

#### 12. Source Oscillation Input at Turning on the Power Supply

At turning on the power supply, never fail to input the clock before cancellation of the oscillation stabilizing waiting.

#### 13. Hardware Stand-by at Turning on the Power Supply

When turning on the power supply with the HST pin being set to "L" level, the hardware doesn't stand by. However the HST pin becomes available after the reset cancellation, the HST pin must once be back to "H" level.

#### 14. Power on Reset

Make sure to make power on reset at turning on the power supply or returning on the power supply when the power supply voltage is below the warranty range for normal operation.

#### 15. Notes on during operation of PLL clock mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self oscillating circuit evevn when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

#### 16. Watchdog timer function

The watchdog timer supported by the FR family monitors the program that performs the reset delay operation for a specified time. If the program hangs and the reset delay operation is not performed, the watchdog timer resets the CPU. Therefore, once the watchdog timer is enabled, operation continues until the CPU is reset. As an exception, a reset delay automatically occurs if the CPU stops program execution.

#### BLOCK DIAGRAM

#### CPU CORE

#### 1. Memory Space

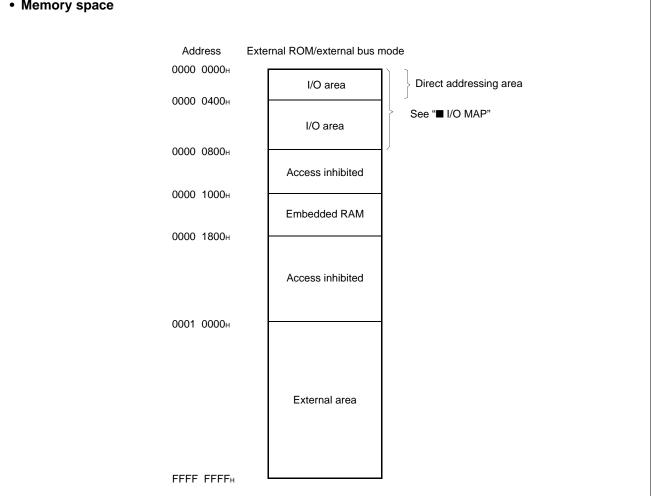

The FR family has a logical address space of 4 Gbytes (2<sup>32</sup> bytes) and the CPU linearly accesses the memory space.

#### • Memory space

#### • Direct addressing area

The following areas on the memory space are assigned to direct addressing area for I/O. In these areas, an address can be specified in a direct operand of a code.

Direct areas consists of the following areas dependent on accessible data sizes.

Byte data access: 000н to 0FFн

Half word data access: 000H to 1FFH

Word data access: 000н to 3FFн

#### 2. Registers

The FR family has two types of registers; dedicated registers embedded on the CPU and general-purpose registers on memory.

#### Dedicated registers

Program counter (PC):32-bit length, indicates the location of the instruction to be executed.Program status (PS):32-bit length, register for storing register pointer or condition codesTable base register (TBR):Holds top address of vector table used in EIT (Exceptional/Interrupt/Trap)processing.

Return pointer (RP): Holds address to resume operation after returning from a subroutine. System stack pointer (SSP): Indicates system stack space.

User's stack pointer (USP): Indicates user's stack space.

Multiplication/division result register (MDH/MDL): 32-bit length, register for multiplication/division

| • 32 bits | _ <b>&gt;</b>                  | Initial                | value         |

|-----------|--------------------------------|------------------------|---------------|

| PC        | Program counter                | XXXX XXXXH             | Indeterminate |

| PS        | Program status                 |                        |               |

| TBR       | Table base register            | 000F FC00н             |               |

| RP        | Return pointer                 | XXXX XXXXH             | Indeterminate |

| SSP       | System stack pointer           | 0000 0000 н            |               |

| USP       | User's stack pointer           | XXXX XXXX <sub>H</sub> | Indeterminate |

| MDH       | Multiplication/division result | XXXX XXXXH             | Indeterminate |

| MDL       | register                       | XXXX XXXXH             | Indeterminate |

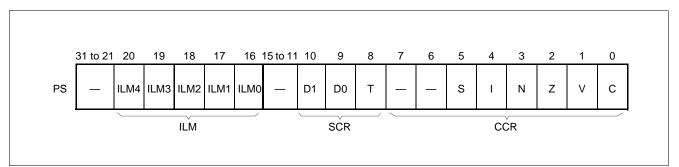

#### • Program status (PS)

The PS register is for holding program status and consists of a condition code register (CCR), a system condition code register (SCR) and a interrupt level mask register (ILM).

#### • Condition code register (CCR)

S-flag: Specifies a stack pointer used as R15.

- I-flag: Controls user interrupt request enable/disable.

- N-flag: Indicates sign bit when division result is assumed to be in the 2's complement format.

- Z-flag: Indicates whether or not the result of division was "0".

- V-flag: Assumes the operand used in calculation in the 2's complement format and indicates whether or not overflow has occurred.

- C-flag: Indicates if a carry or borrow from the MSB has occurred.

#### • System condition code register (SCR)

T-flag: Specifies whether or not to enable step trace trap.

#### • Interrupt level mask register (ILM)

ILM4 to ILM0: Register for holding interrupt level mask value. The value held by this register is used as a level mask. When an interrupt request issued to the CPU is higher than the level held by ILM, the interrupt request is accepted.

| ILM4 | ILM3 | ILM2 | ILM1 | ILMO | Interrupt level | High-low |

|------|------|------|------|------|-----------------|----------|

| 0    | 0    | 0    | 0    | 0    | 0               | High     |

|      |      | :    |      | •    | :               | <b>A</b> |

|      |      | :    |      |      | :               |          |

| 0    | 1    | 0    | 0    | 0    | 15              |          |

|      |      | :    |      |      | :               |          |

|      |      | :    |      |      | :               | +        |

| 1    | 1    | 1    | 1    | 1    | 31              | Low      |

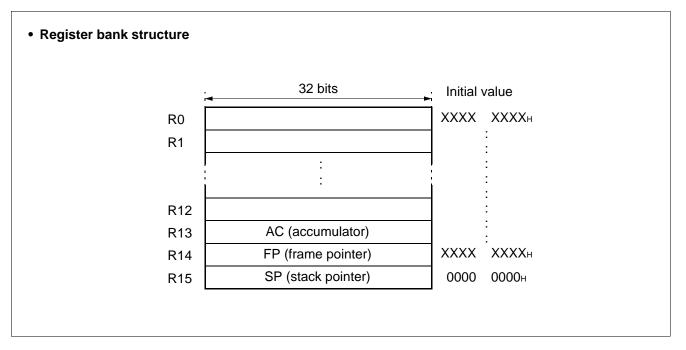

#### GENERAL-PURPOSE REGISTERS

R0 to R15 are general-purpose registers embedded on the CPU. These registers functions as an accumulator and a memory access pointer (field for indicating address).

Of the above 16 registers, following registers have special functions. To support the special functions, part of the instruction set has been sophisticated to have enhanced functions.

R13: Virtual accumulator (AC)

R14: Frame pointer (FP)

R15: Stack pointer (SP)

Upon reset, values in R0 to R14 are not fixed. Value in R15 is initialized to be 0000 0000H (SSP value).

#### SETTING MODE

#### 1. Pin

• Mode setting pins and modes

| Mo  | Mode setting<br>pins |     | Mode name              | Reset vector<br>access area | External data<br>bus width | Bus mode                  |  |

|-----|----------------------|-----|------------------------|-----------------------------|----------------------------|---------------------------|--|

| MD2 | MD1                  | MD0 |                        | access area                 | bus width                  |                           |  |

| 0   | 0                    | 0   | External vector mode 0 | External                    | 8 bits                     | External ROM/external bus |  |

| 0   | 0                    | 1   | External vector mode 1 | External                    | 16 bits                    | mode                      |  |

| 0   | 1                    | 0   | —                      | —                           | —                          | Inhibited                 |  |

| 0   | 1                    | 1   | Internal vector mode   | Internal                    | (Mode register)            | Single-chip mode*         |  |

| 1   | _                    | —   | —                      | —                           | —                          | Inhibited                 |  |

\*: The MB91101 and MB91101A do not support single-chip mode.

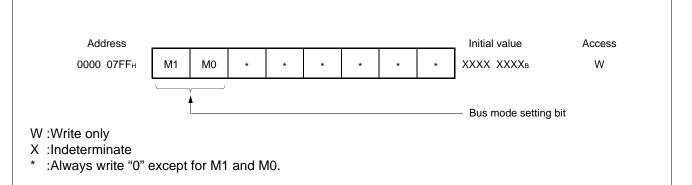

#### 2. Registers

#### Mode setting registers (MODR) and modes

#### • Bus mode setting bits and functions

| M1 | MO | Functions                      | Note      |

|----|----|--------------------------------|-----------|

| 0  | 0  | Single-chip mode               |           |

| 0  | 1  | Internal ROM/external bus mode |           |

| 1  | 0  | External ROM/external bus mode |           |

| 1  | 1  | —                              | Inhibited |

Note: Because of without internal ROM, the MB91101 and MB91101A allow "10<sup>B</sup>" setting value only.

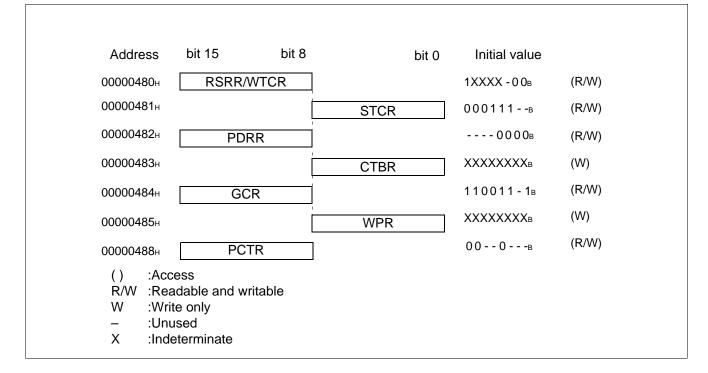

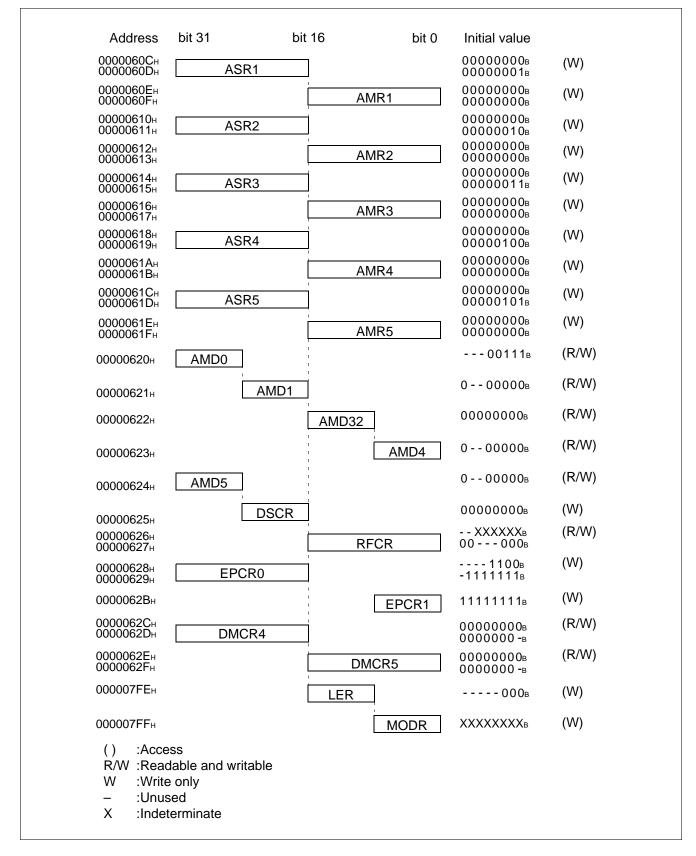

#### ■ I/O MAP

| Address              | Abbreviation | Register name                                    | Read/write | Initial value |  |  |

|----------------------|--------------|--------------------------------------------------|------------|---------------|--|--|

| 0000н                |              | (Reserved)                                       |            |               |  |  |

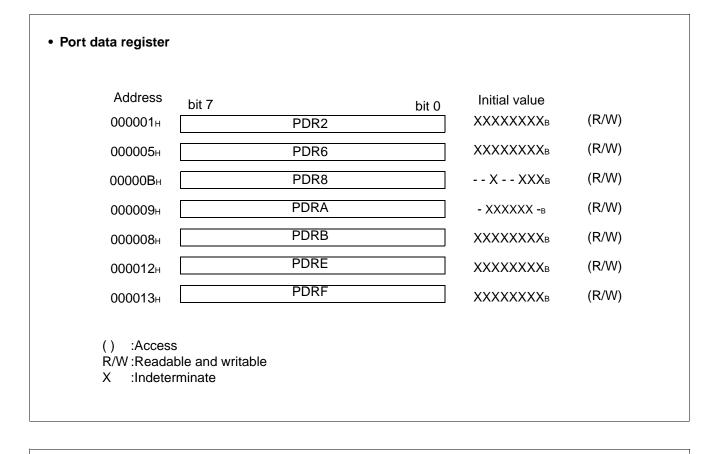

| 0001н                | PDR2         | Port 2 data register                             | R/W        | XXXXXXXXB     |  |  |

| 0002н<br>to<br>0004н |              | (Reserved)                                       |            |               |  |  |

| 0005н                | PDR6         | Port 6 data register                             | R/W        | XXXXXXXXB     |  |  |

| 0006н                |              | (Decentred))                                     |            |               |  |  |

| 0007н                | -            | (Reserved)                                       |            |               |  |  |

| 0008н                | PDRB         | Port B data register                             | R/W        | XXXXXXXXB     |  |  |

| 0009н                | PDRA         | Port A data register                             | R/W        | _ XXXXXX _B   |  |  |

| 000Ан                |              | (Reserved)                                       |            |               |  |  |

| 000Вн                | PDR8         | Port 8 data register                             | R/W        | XXXXB         |  |  |

| 000Сн<br>to<br>0011н | (Reserved)   |                                                  |            |               |  |  |

| 0012н                | PDRE         | Port E data register                             | R/W        | XXXXXXXXB     |  |  |

| 0013н                | PDRF         | Port F data register                             | R/W        | XXXXXXXXB     |  |  |

| 0014н<br>to<br>001Вн |              | (Reserved)                                       |            |               |  |  |

| 001Cн                | SSR0         | Serial status register 0                         | R/W        | 00001_00в     |  |  |

| 001Dн                | SIDR0/SODR0  | Serial input register 0/serial output register 0 | R/W        | XXXXXXXXB     |  |  |

| <b>001Е</b> н        | SCR0         | Serial control register 0                        | R/W        | 00000100в     |  |  |

| 001Fн                | SMR0         | Serial mode register 0                           | R/W        | 0000_0        |  |  |

| 0020н                | SSR1         | Serial status register 1                         | R/W        | 00001_00в     |  |  |

| 0021н                | SIDR1/SODR1  | Serial input register 1/serial output register 1 | R/W        | XXXXXXXXB     |  |  |

| 0022н                | SCR1         | Serial control register 1                        | R/W        | 00000100в     |  |  |

| 0023н                | SMR2         | Serial mode register 1                           | R/W        | 0000_0        |  |  |

| 0024н                | SSR2         | Serial status register 2                         | R/W        | 00001_00в     |  |  |

| 0025н                | SIDR2/SODR2  | Serial input register 2/serial output register 2 | R/W        | XXXXXXXXB     |  |  |

| 0026н                | SCR2         | Serial control register 2                        | R/W        | 00000100в     |  |  |

| 0027н                | SMR2         | Serial mode register 2                           | R/W        | 0000_         |  |  |

| Address              | Abbreviation | Register name                               | Read/write | Initial value |  |  |  |  |

|----------------------|--------------|---------------------------------------------|------------|---------------|--|--|--|--|

| 0028н                |              | 40 bit related as vistan ab 0               | 207        | XXXXXXXX      |  |  |  |  |

| 0029н                | TMRLR0       | 16-bit reload register ch. 0                | W          | XXXXXXXXB     |  |  |  |  |

| 002Ан                |              |                                             | 5          | XXXXXXXXB     |  |  |  |  |

| 002Вн                | - TMR0       | 16-bit timer register ch. 0                 | R          | XXXXXXXXB     |  |  |  |  |

| 002Сн                |              |                                             |            |               |  |  |  |  |

| 002Dн                | -            | (Reserved)                                  |            |               |  |  |  |  |

| <b>002Е</b> н        | T10000       | 16-bit reload timer control status register |            | 0000в         |  |  |  |  |

| 002Fн                | TMCSR0       | ch. 0                                       | R/W        | 00000000      |  |  |  |  |

| 0030н                |              |                                             |            | XXXXXXXXB     |  |  |  |  |

| 0031н                | - TMRLR1     | 16-bit reload register ch. 1                | W          | XXXXXXXXB     |  |  |  |  |

| 0032H                |              |                                             | _          | XXXXXXXXB     |  |  |  |  |

| 0033н                | - TMR1       | 16-bit timer register ch. 1                 | R          | XXXXXXXXB     |  |  |  |  |

| 0034н                |              |                                             |            |               |  |  |  |  |

| 0035н                | -            | (Reserved)                                  |            |               |  |  |  |  |

| 0036н                |              | 16-bit reload timer control status register |            | 0000в         |  |  |  |  |

| 0037н                | TMCSR1       | ch. 1                                       | R/W        | 00000000      |  |  |  |  |

| 0038н                |              |                                             | _          | XХв           |  |  |  |  |

| 0039н                | ADCR         | A/D converter data register                 | R          | XXXXXXXXB     |  |  |  |  |

| 003Ан                | 1200         |                                             | 5 4 4      | 00000000      |  |  |  |  |

| 003Вн                | ADCS         | A/D converter control status register       | R/W        | 00000000      |  |  |  |  |

| 003Сн                |              |                                             |            | XXXXXXXXB     |  |  |  |  |

| 003Dн                | - TMRLR2     | 16-bit reload register ch. 2                | W          | XXXXXXXXB     |  |  |  |  |

| 003Eн                |              |                                             | _          | XXXXXXXXB     |  |  |  |  |

| 003Fн                | TMR2         | 16-bit timer register ch. 2                 | R          | XXXXXXXX      |  |  |  |  |

| 0040н                |              |                                             | I          |               |  |  |  |  |

| 0041н                |              | (Reserved)                                  |            |               |  |  |  |  |

| 0042н                | T10000       | 16-bit reload timer control status register | D AAA      | 0000в         |  |  |  |  |

| 0043н                | TMCSR2       | ch. 2                                       | R/W        | 00000000      |  |  |  |  |

| 0044н<br>to<br>0077н |              | (Reserved)                                  |            | (Continued    |  |  |  |  |

| Address              | Abbreviation | Register name                                     | Read/write | Initial value |  |  |  |  |  |

|----------------------|--------------|---------------------------------------------------|------------|---------------|--|--|--|--|--|

| 0078н                |              |                                                   | DAA        | 00000000      |  |  |  |  |  |

| 0079н                | UTIM0/UTIMR0 | U-TIMER register ch. 0/reload register ch. 0      | R/W        | 00000000      |  |  |  |  |  |

| 007Ан                | (Reserved)   |                                                   |            |               |  |  |  |  |  |

| 007Вн                | UTIMC0       | U-TIMER control register ch. 0                    | R/W        | 000001в       |  |  |  |  |  |

| 007Сн                |              |                                                   | DAA        | 00000000      |  |  |  |  |  |

| 007Dн                | UTIM1/UTIMR1 | U-TIMER register ch. 1/reload register ch. 1      | R/W        | 00000000      |  |  |  |  |  |

| <b>007Е</b> н        |              | (Reserved)                                        |            |               |  |  |  |  |  |

| <b>007F</b> н        | UTIMC1       | U-TIMER control register ch. 1                    | R/W        | 00001в        |  |  |  |  |  |

| 0080н                |              |                                                   | DAA        | 00000000      |  |  |  |  |  |

| <b>0081</b> H        | UTIM2/UTIMR2 | U-TIMER register ch. 2/reload register ch. 2      | R/W        | 000000000     |  |  |  |  |  |

| 0082н                |              | (Reserved)                                        |            |               |  |  |  |  |  |

| 0083н                | UTIMC2       | U-TIMER control register ch. 2                    | R/W        | 000001в       |  |  |  |  |  |

| 0084н<br>to<br>0093н | (Reserved)   |                                                   |            |               |  |  |  |  |  |

| 0094н                | EIRR         | External interrupt cause register                 | R/W        | 00000000      |  |  |  |  |  |

| 0095н                | ENIR         | Interrupt enable register                         | R/W        | 00000000      |  |  |  |  |  |

| 0096н<br>to<br>0098н |              | (Reserved)                                        |            |               |  |  |  |  |  |

| 0099н                | ELVR         | External interrupt request level setting register | R/W        | 000000000     |  |  |  |  |  |

| 009Ан<br>to<br>00D1н |              | (Reserved)                                        |            |               |  |  |  |  |  |

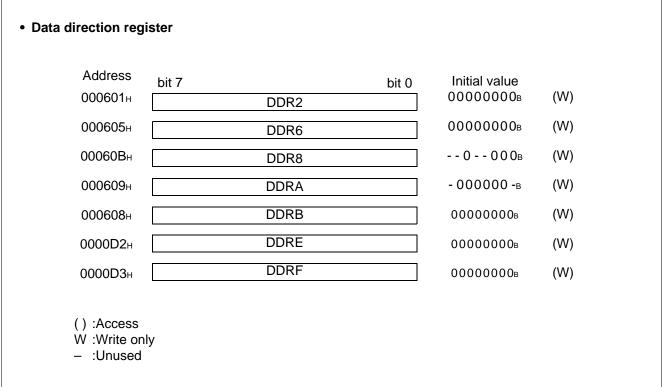

| 00D2н                | DDRE         | Port E data direction register                    | W          | 00000000      |  |  |  |  |  |

| 00D3н                | DDRF         | Port F data direction register                    | W          | 000000000     |  |  |  |  |  |

| 00D4н<br>to<br>00DBн | (Reserved)   |                                                   |            |               |  |  |  |  |  |

| 00DCн                | 00014        |                                                   | D 444      | 00110010в     |  |  |  |  |  |

| 00DDн                | - GCN1       | General control register 1                        | R/W        | 0001000в      |  |  |  |  |  |

| 00DEн                |              | (Reserved)                                        | 1          |               |  |  |  |  |  |

| 00DFн                | GCN2         | General control register 2                        | R/W        | 00000000      |  |  |  |  |  |

| Address       | Abbreviation | Register name                   | Read/write | Initial value         |

|---------------|--------------|---------------------------------|------------|-----------------------|

| 00E0н         | DTMDO        |                                 | D          | 11111111              |

| 00E1н         | - PTMR0      | Ch. 0 timer register            | R          | 11111111              |

| 00E2н         | DOODA        |                                 | 10/        | XXXXXXXXB             |

| 00E3н         | PCSR0        | Ch. 0 cycle setting register    | W          | XXXXXXXXB             |

| 00E4н         |              |                                 | 10/        | XXXXXXXXB             |

| 00E5н         | - PDUT0      | Ch. 0 duty setting register     | W          | XXXXXXXXB             |

| 00E6н         | PCNH0        | Ch. 0 control status register H | R/W        | 000000_в              |

| 00E7н         | PCNL0        | Ch. 0 control status register L | R/W        | 00000000              |

| 00E8н         |              |                                 | R          | 11111111              |

| 00E9н         | - PTMR1      | Ch. 1 timer register            |            | 11111111              |

| 00EAн         | 50054        |                                 |            | XXXXXXXXB             |

| 00EBн         | PCSR1        | Ch. 1 cycle setting register    | W          | XXXXXXXXB             |

| 00ECн         |              | Ch. 1 duty setting register W   |            | XXXXXXXXB             |

| 00EDн         | - PDUT1      |                                 |            | XXXXXXXXB             |

| 00EEн         | PCNH1        | Ch. 1 control status register H | R/W        | 000000_в              |

| 00EFн         | PCNL1        | Ch. 1 control status register L | R/W        | 00000000              |

| 00F0н         | DTMDO        |                                 | 5          | 11111111              |

| <b>00F1</b> н | - PTMR2      | Ch. 2 timer register            | R          | 11111111              |

| 00F2н         | DOODO        |                                 | 207        | XXXXXXXXB             |

| 00F3н         | PCSR2        | Ch. 2 cycle setting register    | W          | XXXXXXXXB             |

| 00F4н         |              |                                 |            | XXXXXXXXB             |

| 00F5⊦         | - PDUT2      | Ch. 2 duty setting register     | W          | XXXXXXXXB             |

| 00F6н         | PCNH2        | Ch. 2 control status register H | R/W        | 000000_в              |

| <b>00F7</b> н | PCNL2        | Ch. 2 control status register L | R/W        | 00000000              |

| 00F8н         | DTMDO        |                                 | D          | 11111111              |

| 00F9н         | - PTMR3      | Ch. 3 timer register            | R          | 11111111 <sub>В</sub> |

| 00FAн         | DOODO        |                                 |            | XXXXXXXXB             |

| 00FBн         | - PCSR3      | Ch. 3 cycle setting register    | W          | XXXXXXXXB             |

| 00FCн         |              |                                 |            | XXXXXXXXB             |

| 00FDн         | - PDUT3      | Ch. 3 duty setting register     | W          | XXXXXXXXB             |

| 00FEн         | PCNH3        | Ch. 3 control status register H | R/W        | 0000000_в             |

| <b>00FF</b> н | PCNL3        | Ch. 3 control status register L | R/W        | 00000000              |

| Address              | Abbreviation | Register name                               | Read/write   | Initial value             |  |  |  |

|----------------------|--------------|---------------------------------------------|--------------|---------------------------|--|--|--|

| 0100н<br>to<br>01FFн | (Reserved)   |                                             |              |                           |  |  |  |

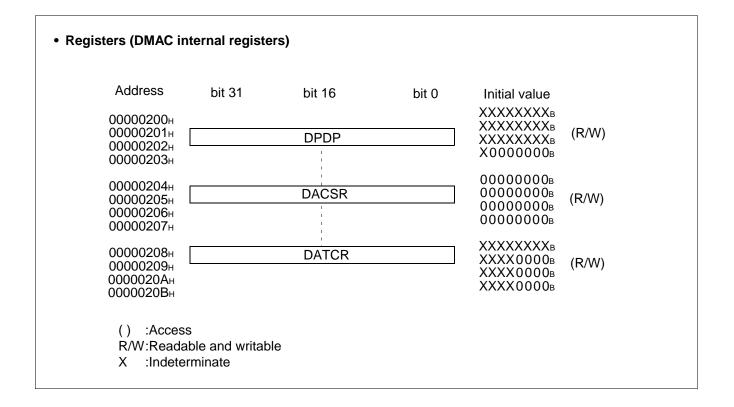

| 0200н                |              |                                             |              | XXXXXXXXB                 |  |  |  |

| 0201н                |              |                                             |              | XXXXXXXXB                 |  |  |  |

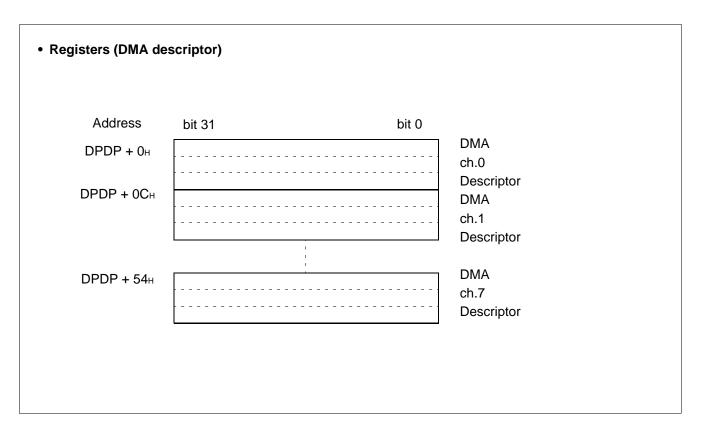

| 0202н                | DPDP         | DMAC parameter descriptor pointer           | R/W          | XXXXXXXXB                 |  |  |  |

| 0203н                | -            |                                             |              | X 0 0 0 0 0 0 0           |  |  |  |

| 0204н                |              |                                             |              | 0 0 0 0 0 0 0 0 0 B       |  |  |  |

| 0205н                |              | DMAC control status register                | R/W          | 0 0 0 0 0 0 0 0 0 B       |  |  |  |

| 0206н                | DACSR        | DMAC control status register                | R/W          | 000000000                 |  |  |  |

| 0207н                | -            |                                             |              | 000000000                 |  |  |  |

| 0208н                |              |                                             |              | XXXXXXXXB                 |  |  |  |

| 0209н                | DATOD        |                                             |              | XXXX 0 0 0 0B             |  |  |  |

| 020Ан                | DATCR        | DMAC pin control register                   | R/W          | XXXX 0 0 0 0B             |  |  |  |

| 020Вн                | -            |                                             |              | XXXX 0 0 0 0 <sub>B</sub> |  |  |  |

| 020Сн<br>to<br>03E3н | (Reserved)   |                                             |              |                           |  |  |  |

| 03E4н                |              |                                             |              | E                         |  |  |  |

| 03E5н                |              | Instruction cache control register          | R/W          | E                         |  |  |  |

| <b>03E6</b> н        | ICHCR        |                                             |              | E                         |  |  |  |

| 03E7н                | -            |                                             |              | 0 0 0 0 0 0 E             |  |  |  |

| 03E8н<br>to<br>03EFн |              | (Reserved)                                  |              |                           |  |  |  |

| 03F0н                |              |                                             |              | XXXXXXXXB                 |  |  |  |

| 03F1н                |              |                                             |              | XXXXXXXX                  |  |  |  |

| 03F2н                | BSD0         | Bit search module 0-detection data register | W            | XXXXXXXXB                 |  |  |  |

| 03F3н                |              |                                             |              | XXXXXXXX                  |  |  |  |

| 03F4⊦                |              |                                             |              | XXXXXXXX                  |  |  |  |

| 03F5н                |              |                                             | <b>D A U</b> | XXXXXXXX                  |  |  |  |

| 03F6н                | BSD1         | Bit search module 1-detection data register | R/W          | XXXXXXXX                  |  |  |  |

| 03F7н                | 1            |                                             |              | XXXXXXXX                  |  |  |  |

| Address       | Abbreviation | Register name                               | Read/write | Initial value      |

|---------------|--------------|---------------------------------------------|------------|--------------------|

| 03F8н         |              |                                             |            | XXXXXXXXB          |

| 03F9н         | BODO         | Bit search module transition-detection data | 14/        | XXXXXXXXB          |

| 03FAн         | BSDC         | register                                    | W          | XXXXXXXX           |

| 03FBн         | -            |                                             |            | XXXXXXXXB          |

| 03FCн         |              |                                             |            | XXXXXXXXB          |

| 03FDн         |              |                                             | XXXXXXXXB  |                    |

| 03FEн         | BSRR         | Bit search module detection result register | R          | XXXXXXXXB          |

| 03FFн         |              |                                             |            | XXXXXXXXB          |

| 0400н         | ICR00        | Interrupt control register 0                | R/W        | 11111              |

| 0401н         | ICR01        | Interrupt control register 1                | R/W        | 11111 <sub>в</sub> |

| 0402н         | ICR02        | Interrupt control register 2                | R/W        | 11111 <sub>в</sub> |

| 0403н         | ICR03        | Interrupt control register 3                | R/W        | 11111              |

| 0404н         | ICR04        | Interrupt control register 4                | R/W        | 11111              |

| 0405н         | ICR05        | Interrupt control register 5                | R/W        | 11111              |